# Fault Tolerant Computer Architecture

Daniel J. Sorin

# Synthesis Lectures on Computer Architecture

# Fault Tolerant Computer Architecture

# Synthesis Lectures on Computer Architecture

#### Editor

## Mark D. Hill, University of Wisconsin, Madison

Synthesis Lectures on Computer Architecture publishes 50 to 150 page publications on topics pertaining to the science and art of designing, analyzing, selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals.

# Fault Tolerant Computer Architecture

Daniel Sorin 2009

# The Datacenter as a Computer: An Introduction to the Design of Warehouse-Scale Machines

Luiz André Barroso and Urs Hölzle 2009

# Computer Architecture Techniques for Power-Efficiency

Stefanos Kaxiras and Margaret Martonosi 2008

# Chip Mutiprocessor Architecture: Techniques to Improve Throughput and Latency

Kunle Olukotun, Lance Hammond, James Laudon 2007

# **Transactional Memory**

James R. Larus, Ravi Rajwar 2007

# **Quantum Computing for Computer Architects**

Tzvetan S. Metodi, Frederic T. Chong 2006

# Copyright © 2009 by Morgan & Claypool

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other except for brief quotations in printed reviews, without the prior permission of the publisher.

Fault Tolerant Computer Architecture Daniel Sorin www.morganclaypool.com

ISBN: 9781598299533 paperback

ISBN: 9781598299540 ebook

DOI: 10.2200/S00192ED1V01Y200904CAC005

A Publication in the Morgan & Claypool Publishers series

SYNTHESIS LECTURES ON COMPUTER ARCHITECTURE

Lecture #5

Series Editor: Mark D. Hill, University of Wisconsin, Madison

Series ISSN

ISSN 1935-3235 print

ISSN 1935-3243 electronic

# Fault Tolerant Computer Architecture

Daniel J. Sorin

Duke University

SYNTHESIS LECTURES ON COMPUTER ARCHITECTURE #5

# **ABSTRACT**

For many years, most computer architects have pursued one primary goal: performance. Architects have translated the ever-increasing abundance of ever-faster transistors provided by Moore's law into remarkable increases in performance. Recently, however, the bounty provided by Moore's law has been accompanied by several challenges that have arisen as devices have become smaller, including a decrease in dependability due to physical faults. In this book, we focus on the dependability challenge and the fault tolerance solutions that architects are developing to overcome it. The two main purposes of this book are to explore the key ideas in fault-tolerant computer architecture and to present the current state-of-the-art—over approximately the past 10 years—in academia and industry.

# **KEYWORDS**

fault tolerance (or fault tolerant), reliability, dependability, computer architecture, error detection, error recovery, fault diagnosis, self-repair, autonomous, dynamic verification

# **Dedication**

"To Deborah, Jason, and Julie"

# Acknowledgments

I would like to thank my family for their support while I was writing this lecture. I would also like to thank Mark Hill for inviting me to write this lecture and Mike Morgan for organizing the production of the lecture. Valuable feedback on early drafts of the lecture was provided by Babak Falsafi, Jude Rivers, and Mark Hill. I would also like to thank Lihao Xu for helping me with a question about error coding.

# Contents

| 1. | Intro | duction | n1                                 |

|----|-------|---------|------------------------------------|

|    | 1.1   | Goals   | of this Book                       |

|    | 1.2   | Faults  | , Errors, and Failures             |

|    |       | 1.2.1   | Masking                            |

|    |       | 1.2.2   | Duration of Faults and Errors      |

|    |       | 1.2.3   | Underlying Physical Phenomena      |

|    | 1.3   | Trend   | s Leading to Increased Fault Rates |

|    |       | 1.3.1   | Smaller Devices and Hotter Chips   |

|    |       | 1.3.2   | More Devices per Processor         |

|    |       | 1.3.3   | More Complicated Designs           |

|    | 1.4   | Error   | Models                             |

|    |       | 1.4.1   | Error Type                         |

|    |       | 1.4.2   | Error Duration                     |

|    |       | 1.4.3   | Number of Simultaneous Errors      |

|    | 1.5   | Fault ' | Tolerance Metrics                  |

|    |       | 1.5.1   | Availability9                      |

|    |       | 1.5.2   | Reliability                        |

|    |       | 1.5.3   | Mean Time to Failure               |

|    |       | 1.5.4   | Mean Time Between Failures         |

|    |       | 1.5.5   | Failures in Time                   |

|    |       | 1.5.6   | Architectural Vulnerability Factor |

|    | 1.6   | The R   | test of This Book                  |

|    | 1.7   | Refere  | ences 13                           |

| 2. | Erro  | r Detec | tion                               |

|    | 2.1   | Gener   | ral Concepts                       |

|    |       | 2.1.1   | Physical Redundancy                |

|    |       | 2.1.2   | Temporal Redundancy                |

|            |      | 2.1.3                | Information Redundancy                            | 22 |

|------------|------|----------------------|---------------------------------------------------|----|

|            |      | 2.1.4                | The End-to-End Argument                           | 25 |

| 2.2        |      | Microprocessor Cores |                                                   |    |

|            |      | 2.2.1                | Functional Units                                  | 27 |

|            |      | 2.2.2                | Register Files                                    | 29 |

|            |      | 2.2.3                | Tightly Lockstepped Redundant Cores               | 29 |

|            |      | 2.2.4                | Redundant Multithreading Without Lockstepping     | 30 |

|            |      | 2.2.5                | Dynamic Verification of Invariants                | 34 |

|            |      | 2.2.6                | High-Level Anomaly Detection                      | 39 |

|            |      | 2.2.7                | Using Software to Detect Hardware Errors          | 41 |

|            |      | 2.2.8                | Error Detection Tailored to Specific Fault Models | 42 |

|            | 2.3  | Cache                | es and Memory                                     | 44 |

|            |      | 2.3.1                | Error Code Implementation                         | 44 |

|            |      | 2.3.2                | Beyond EDCs                                       | 45 |

|            |      | 2.3.3                | Detecting Errors in Content Addressable Memories  | 46 |

|            |      | 2.3.4                | Detecting Errors in Addressing                    | 47 |

|            | 2.4  | Multij               | processor Memory Systems                          | 48 |

|            |      | 2.4.1                | Dynamic Verification of Cache Coherence           | 49 |

|            |      | 2.4.2                | Dynamic Verification of Memory Consistency        | 50 |

|            |      | 2.4.3                | Interconnection Networks                          | 52 |

|            | 2.5  | Concl                | lusions                                           | 52 |

|            | 2.6  | Refere               | ences                                             | 52 |

| 3.         | Erro | r Recov              | /ery                                              | 61 |

| <i>J</i> . | 3.1  |                      | ral Concepts                                      |    |

|            | 3.1  | 3.1.1                | Forward Error Recovery                            |    |

|            |      | 3.1.2                | Backward Error Recovery                           |    |

|            |      | 3.1.3                | Comparing the Performance of FER and BER          |    |

|            | 3.2  |                      | oprocessor Cores                                  |    |

|            |      | 3.2.1                | 1                                                 |    |

|            |      | 3.2.2                | BER for Cores                                     |    |

|            | 3.3  |                      | e-Core Memory Systems                             |    |

|            |      | _                    | FER for Caches and Memory                         |    |

|            |      |                      | BER for Caches and Memory                         |    |

|            | 3.4  |                      | Unique to Multiprocessors                         |    |

|            |      |                      |                                                   |    |

|    |       | 3.4.1 What State to Save for the Recovery Point            | 74 |

|----|-------|------------------------------------------------------------|----|

|    |       | 3.4.2 Which Algorithm to Use for Saving the Recovery Point | 74 |

|    |       | 3.4.3 Where to Save the Recovery Point                     | 75 |

|    |       | 3.4.4 How to Restore the Recovery Point State              | 75 |

|    | 3.5   | Software-Implemented BER                                   | 75 |

|    | 3.6   | Conclusions                                                | 76 |

|    | 3.7   | References                                                 |    |

| 4. | Diag  | gnosis                                                     | 81 |

|    | 4.1   | General Concepts                                           | 81 |

|    |       | 4.1.1 The Benefits of Diagnosis                            | 81 |

|    |       | 4.1.2 System Model Implications                            | 82 |

|    |       | 4.1.3 Built-In Self-Test                                   |    |

|    | 4.2   | Microprocessor Core                                        | 83 |

|    |       | 4.2.1 Using Periodic BIST                                  | 83 |

|    |       | 4.2.2 Diagnosing During Normal Execution                   | 84 |

|    | 4.3   | Caches and Memory                                          | 85 |

|    | 4.4   | Multiprocessors                                            | 85 |

|    | 4.5   | Conclusions                                                | 86 |

|    | 4.6   | References                                                 | 86 |

| 5. | Self- | -Repair                                                    | 89 |

|    | 5.1   | General Concepts                                           | 89 |

|    | 5.2   | Microprocessor Cores                                       | 90 |

|    |       | 5.2.1 Superscalar Cores                                    | 90 |

|    |       | 5.2.2 Simple Cores                                         | 91 |

|    | 5.3   | Caches and Memory                                          | 91 |

|    | 5.4   | Multiprocessors                                            | 92 |

|    |       | 5.4.1 Core Replacement                                     | 92 |

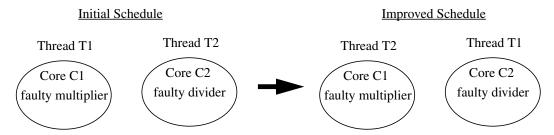

|    |       | 5.4.2 Using the Scheduler to Hide Faulty Functional Units  |    |

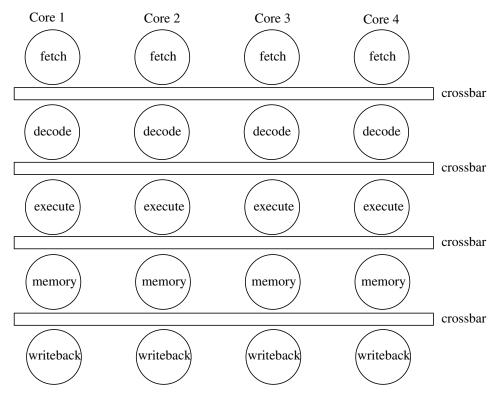

|    |       | 5.4.3 Sharing Resources Across Cores                       |    |

|    |       | 5.4.4 Self-Repair of Noncore Components                    |    |

|    | 5.5   | Conclusions                                                |    |

|    | 5.6   | References                                                 | 95 |

| 6.  | The    | The Future |                                                          | 99  |

|-----|--------|------------|----------------------------------------------------------|-----|

|     | 6.1    | Adopt      | tion by Industry                                         | 99  |

|     |        | -          | e Relationships Between Fault Tolerance and Other Fields |     |

|     |        | 6.2.1      | Power and Temperature                                    | 100 |

|     |        | 6.2.2      | Security                                                 | 100 |

|     |        | 6.2.3      | Static Design Verification                               | 100 |

|     |        | 6.2.4      | Fault Vulnerability Reduction                            | 100 |

|     |        | 6.2.5      | Tolerating Software Bugs                                 | 101 |

|     | 6.3    | Refere     | ences                                                    | 101 |

| Aut | hor Bi | ography    | 7                                                        | 103 |

# Introduction

For many years, most computer architects have pursued one primary goal: performance. Architects have translated the ever-increasing abundance of ever-faster transistors provided by Moore's law into remarkable increases in performance. Recently, however, the bounty provided by Moore's law has been accompanied by several challenges that have arisen as devices have become smaller, including a decrease in dependability due to physical faults. In this book, we focus on the dependability challenge and the fault tolerance solutions that architects are developing to overcome it.

The goal of a fault-tolerant computer is to provide *safety* and *liveness*, despite the possibility of faults. A *safe* computer never produces an incorrect user-visible result. If a fault occurs, the computer hides its effects from the user. Safety alone is not sufficient, however, because it does not guarantee that the computer does anything useful. A computer that is disconnected from its power source is safe—it cannot produce an incorrect user-visible result—yet it serves no purpose. A *live* computer continues to make forward progress, even in the presence of faults. Ideally, architects design computers that are both safe and live, even in the presence of faults. However, even if a computer cannot provide liveness in all fault scenarios, maintaining safety in those situations is still extremely valuable. It is preferable for a computer to stop doing anything rather than to produce incorrect results. An often used example of the benefits of safety, even if liveness cannot be ensured, is an automatic teller machine (ATM). In the case of a fault, the bank would rather the ATM shut itself down instead of dispensing incorrect amounts of cash.

## 1.1 GOALS OF THIS BOOK

The two main purposes of this book are to explore the key ideas in fault-tolerant computer architecture and to present the current state-of-the-art—over approximately the past 10 years—in academia and industry. We must be aware, though, that fault-tolerant computer architecture is not a new field. For specific computing applications that require extreme reliability—including medical equipment, avionics, and car electronics—fault tolerance is always required, regardless of the likelihood of faults. In these domains, there are canonical, well-studied fault tolerance solutions, such as triple modular redundancy (TMR) or the more general N-modular redundancy (NMR) first proposed by von Neumann [45]. However, for most computing applications, the price of such heavyweight, macro-scale redundancy—in terms of hardware, power, or performance—outweighs

its benefits, particularly when physical faults are relatively uncommon. Although this book does not delve into the details of older systems, we do highlight which key ideas originated in earlier systems. We strongly encourage interested readers to learn more about these historical systems, from both classic textbooks [27, 36] and survey papers [33].

# 1.2 FAULTS, ERRORS, AND FAILURES

Before we explore how to tolerate faults, we must first understand the faults themselves. In this section, we discuss faults and their causes. In Section 1.3, we will discuss the trends that are leading to increasing fault rates.

We consider a *fault* to be a physical flaw, such as a broken wire or a transistor with a gate oxide that has broken down. A fault can manifest itself as an *error*, such as a bit that is a zero instead of a one, or the effect of the fault can be *masked* and not manifest itself as any error. Similarly, an error can be masked or it can result in a user-visible incorrect behavior called a *failure*. Failures include incorrect computations and system hangs.

# 1.2.1 Masking

Masking occurs at several levels—such as faults that do not become errors and errors that do not become failures—and it occurs because of several reasons, including the following.

Logical masking. The effect of an error may be logically masked. For example, if a two-input AND gate has an error on one input and a zero on its other input, the error cannot propagate and cause a failure.

Architectural masking. The effect of an error may never propagate to architectural state and thus never become a user-visible failure. For example, an error in the destination register specifier of a NOP instruction will have no architectural impact. We discuss in Section 1.5 the concept of architectural vulnerability factor (AVF) [23], which is a metric for quantifying what fraction of errors in a given component are architecturally masked.

Application masking. Even if an error does impact architectural state and thus becomes a user-visible failure, the failure might never be observed by the application software running on the processor. For example, an error that changes the value at a location in memory is user-visible; however, if the application never accesses that location or writes over the erroneous value before reading it again, then the failure is masked.

Masking is an important issue for architects who are designing fault-tolerant systems. Most importantly, an architect can devote more resources (hardware and the power it consumes) and effort (design time) toward tolerating faults that are less likely to be masked. For example, there is no need to devote resources to tolerating faults that affect a branch prediction. The worst-case result of

such a fault is a branch misprediction, and the misprediction's effects will be masked by the existing logic that recovers from mispredictions that are not due to faults.

## 1.2.2 Duration of Faults and Errors

Faults and errors can be transient, permanent, or intermittent in nature.

Transient. A transient fault occurs once and then does not persist. An error due to a transient fault is often referred to as a soft error or single event upset.

Permanent. A permanent fault, which is often called a hard fault, occurs at some point in time, perhaps even introduced during chip fabrication, and persists from that time onward. A single permanent fault is likely to manifest itself as a repeated error, unless the faulty component is repaired, because the faulty component will continue to be used and produce erroneous results.

Intermittent. An intermittent fault occurs repeatedly but not continuously in the same place in the processor. As such, an intermittent fault manifests itself via intermittent errors.

The classification of faults and errors based on duration serves a useful purpose. The approach to tolerating a fault depends on its duration. Tolerating a permanent fault requires the ability to avoid using the faulty component, perhaps by using a fault-free replica of that component. Tolerating a transient fault requires no such self-repair because the fault will not persist. Fault tolerance schemes tend to treat intermittent faults as either transients or permanents, depending on how often they recur, although there are a few schemes designed specifically for tolerating intermittent faults [48].

# 1.2.3 Underlying Physical Phenomena

There are many physical phenomena that lead to faults, and we discuss them now based on their duration. Where applicable, we discuss techniques for reducing the likelihood of these physical phenomena leading to faults. Fault avoidance techniques are complementary to fault tolerance.

Transient phenomena. There are two well-studied causes of transient faults, and we refer the interested reader to the insightful historical study by Ziegler et al. [50] of IBM's experiences with soft errors. The first cause is cosmic radiation [49]. The cosmic rays themselves are not the culprits but rather the high-energy particles that are produced when cosmic rays impact the atmosphere. A computer can theoretically be shielded from these high-energy particles (at an extreme, by placing the computer in a cave), but such shielding is generally impractical. The second source of transient faults is alpha particles [22], which are produced by the natural decay of radioactive isotopes. The source of these radioactive isotopes is often, ironically, metal in the chip packaging itself. If a highenergy cosmic ray-generated particle or alpha particle strikes a chip, it can dislodge a significant amount of charge (electrons and holes) within the semiconductor material. If this charge exceeds the critical charge, often denoted Q<sub>crit</sub>, of an SRAM or DRAM cell or p-n junction, it can flip the

value of that cell or transistor output. Because the disruption is a one-time, transient event, the error will disappear once the cell or transistor's output is overwritten.

Transient faults can occur for reasons other than the two best-known causes described above. One possible source of transient faults is electromagnetic interference (EMI) from outside sources. A chip can also create its own EMI, which is often referred to as "cross-talk." Another source of transient errors is supply voltage droops due to large, quick changes in current draw. This source of errors is often referred to as the "dI/dt problem" because it depends on the current changing (dI) in a short amount of time (dt). Architects have recently explored techniques for reducing dI/dt, such as by managing the activity of the processor to avoid large changes in activity [26].

Permanent phenomena. Sources of permanent faults can be placed into three categories.

- 1. Physical wear-out: A processor in the field can fail because of any of several physical wear-out phenomena. A wire can wear out because of electromigration [7, 13, 18, 19]. A transistor's gate oxide can break down over time [6, 10, 21, 24, 29, 41]. Other physical phenomena that lead to permanent wear-outs include thermal cycling and mechanical stress. Many of these wear-out phenomena are exacerbated by increases in temperature. The RAMP model of Srinivasan et al. [40] provides an excellent tutorial on these four phenomena and a model for predicting their impacts on future technologies. The dependence of wear-out on temperature is clearly illustrated in the equations of the RAMP model.

- There has recently been a surge of research in techniques for avoiding wear-out faults. The group that developed the RAMP model [40] proposed the idea of lifetime reliability management [39]. The key insight of this work is that a processor can manage itself to achieve a lifetime reliability goal. A processor can use the RAMP model to estimate its expected lifetime and adjust itself—for example, by reducing its voltage and frequency—to either extend its lifetime (at the expense of performance) or improve its performance (at the expense of lifetime reliability). Subsequent research has proposed avoiding wear-out faults by using voltage and frequency scaling [42], adaptive body biasing [44], and by scheduling tasks on cores in a wear-out-aware fashion [12, 42, 44]. Other research has proposed techniques to avoid specific wear-out phenomena, such as negative bias temperature instability [1, 34]. More generally, dynamic temperature management [37] can help to alleviate the impact of wear-out phenomena that are exacerbated by increasing temperatures.

- 2. Fabrication defects: The fabrication of chips is an imperfect process, and chips may be manufactured with inherent defects. These defects may be detected by post-fabrication, preshipment testing, in which case the defect-induced faults are avoided in the field. However, defects may not reveal themselves until the chip is in the field. One particular concern for post-fabrication testing is that increasing leakage currents are making *I*<sub>DDQ</sub> and burn-in testing infeasible [5, 31].

- For the purposes of designing a fault tolerance scheme, fabrication defects are identical to wear-out faults, except that (a) they occur at time zero and (b) they are much more likely to occur "simultaneously"—that is, having multiple fabrication defects in a single chip is far more likely than having multiple wear-out faults occur at the same instant in the field.

- 3. Design bugs: Because of design bugs, even a perfectly fabricated chip may not behave correctly in all situations. Some readers may recall the infamous floating point division bug in the Intel Pentium processor [4], but it is by no means the only example of a bug in a shipped processor. Industrial validation teams try to uncover as many bugs as possible before fabrication, to avoid having these bugs manifest themselves as faults in the field, but the complete validation of a nontrivial processor is an intractable problem [3]. Despite expending vast resources on validation, there are still many bugs in recently shipped processors [2, 15-17]. Designing a scheme to tolerate design bugs poses some unique challenges, relative to other types of faults. Most notably, homogeneous spatial redundancy (e.g., TMR) is ineffective; all three replicas will produce the same erroneous result due to a design bug because the bug is present in all three replicas.

Intermittent phenomena. Some physical phenomena may lead to intermittent faults. The canonical example is a loose connection. As the chip temperature varies, a connection between two wires or devices may be more or less resistive and more closely model an open circuit or a faultfree connection, respectively. Recently, intermittent faults have been identified as an increasing threat largely due to temperature and voltage fluctuations, as well as prefailure component wearout [8].

#### 1.3 TRENDS LEADING TO INCREASED **FAULT RATES**

Fault-tolerant computer architecture has enjoyed a recent renaissance in response to several trends that are leading toward an increasing number of faults in commodity processors.

# **Smaller Devices and Hotter Chips**

The dimensions of transistors and wires directly affect the likelihood of faults, both transient and permanent. Furthermore, device dimensions impact chip temperature, and temperature has a strong impact on the likelihood of permanent faults.

Transient faults. Smaller devices tend to have smaller critical charges,  $Q_{crit}$ , and we discussed in "Transient Phenomena" from Section 1.2.3 how decreasing  $Q_{crit}$  increases the probability that a high-energy particle strike can disrupt the charge on the device. Shivakumar et al. [35] analyzed the transient error trends for smaller transistors and showed that transient errors will become far more

numerous in the future. In particular, they expect the transient error rate for combinational logic to increase dramatically and even overshadow the transient error rates for SRAM and DRAM.

Permanent faults. Smaller devices and wires are more susceptible to a variety of permanent faults, and this susceptibility is greatly exacerbated by process variability [5]. Fabrication using photolithography is an inherently imperfect process, and the dimensions of fabricated devices and wires may stray from their expected values. In previous generations of CMOS technology, this variability was mostly lost in the noise. A 2-nm variation around a 250-nm expected dimension is insignificant. However, as expected dimensions become smaller, variability's impact becomes more pronounced. A 2-nm variation around a 20-nm expected dimension can lead to a noticeable impact on behavior. Given smaller dimensions and greater process variability, there is an increasing likelihood of wires that are too small to support the required current density and transistor gate oxides that are too thin to withstand the voltages applied across them.

Another factor causing an increase in permanent faults is temperature. For a given chip area, trends are leading toward a greater number of transistors, and these transistors are consuming increasing amounts of active and static (leakage) power. This increase in power consumption per unit area translates into greater temperatures, and the RAMP model of Srinivasan et al. [40] highlights how increasing temperatures greatly exacerbate several physical phenomena that cause permanent faults. Furthermore, as the temperature increases, the leakage current increases, and this positive feedback loop with temperature and leakage current can have catastrophic consequences for a chip.

# 1.3.2 More Devices per Processor

Moore's law has provided architects with ever-increasing numbers of transistors per processor chip. With more transistors, as well as more wires connecting them, there are more opportunities for faults both in the field and during fabrication. Given even a constant fault rate for a single transistor, which is a highly optimistic and unrealistic assumption, the fault rate of a processor is increasing proportionately to the number of transistors per processor. Intuitively, the chances of one billion transistors all working correctly are far less than the probability of one million transistors all working correctly. This trend is unaffected by the move to multicore processors; it is the sheer number of devices per processor, not per core, that leads to more opportunities for faults.

# 1.3.3 More Complicated Designs

Processor designs have historically become increasingly complicated. Given an increasing number of transistors with which to work, architects have generally found innovative ways to modify microarchitectures to extract more performance. Cores, in particular, have benefitted from complex features such as dynamic scheduling (out-of-order execution), branch prediction, speculative load-

store disambiguation, prefetching, and so on. An Intel Pentium 4 core is far more complicated than the original Pentium. This trend may be easing or even reversing itself somewhat because of power limitations—for example, Sun Microsystems' UltraSPARC T1 and T2 processors consist of numerous simple, in-order cores—but even processors with simple cores are likely to require complicated memory systems and interconnection networks to provide the cores with sufficient instruction and data bandwidth.

The result of increased processor complexity is a greater likelihood of design bugs eluding the validation process and escaping into the field. As discussed in "Permanent Phenomena" from Section 1.2.3 design bugs manifest themselves as permanent, albeit rarely exercised, faults. Thus, increasing design complexity is another contributor to increasing fault rates.

#### **ERROR MODELS** 1.4

Architects must be aware of the different types of faults that can occur, and they should understand the trends that are leading to increasing numbers of faults. However, architects rarely need to consider specific faults when they design processors. Intuitively, architects care about the possible errors that may occur, not the underlying physical phenomena. For example, an architect might design a cache frame such that it tolerates a single bit-flip error in the frame, but the architect's fault tolerance scheme is unlikely to be affected by which faults could cause a single bit-flip error.

Rather than explicitly consider every possible fault and how they could manifest themselves as errors, architects generally use error models. An error model is a simple, tractable tool for analyzing a system's fault tolerance. An example of an error model is the well-known "stuck-at" model, which models the impact of faults that cause a circuit value to be stuck at either 0 or 1. There are many underlying physical phenomena that can be represented with the stuck-at model, including some short and open circuits. The benefit of using an error model, such as the stuck-at model, instead of considering the possible physical phenomena, is that architects can design systems to tolerate errors within a set of error models. One challenge with error modeling, as with all modeling, is the issue of "garbage in, garbage out." If the error model is not representative of the errors that are likely to occur, then designing systems to tolerate these errors is not useful. For example, if we assume a stuck-at model for bits in a cache frame but an underlying physical fault causes a bit to instead take on the value of a neighboring bit, then our fault tolerance scheme may be ineffective.

There are many different error models, and we can classify them along three axes: type of error, error duration, and number of simultaneous errors.

# 1.4.1 Error Type

The stuck-at model is perhaps the best-known error model for two reasons. First, it represents a wide range of physical faults. Second, it is easy to understand and use. An architect can easily

enumerate all possible stuck-at errors and analyze how well a fault tolerance scheme handles every possible error.

However, the stuck-at model does not represent the effects of many physical phenomena and thus cannot be used in all situations. If an architect uses the stuck-at error model when developing a fault tolerance scheme, then faults that do not manifest themselves as stuck-at errors may not be tolerated. If these faults are likely, then the system will be unreliable. Thus, other error models have been developed to represent the different erroneous behaviors that would result from underlying physical faults that do not manifest themselves as stuck-at errors.

One low-level error model, similar to stuck-at errors, is *bridging errors* (also known as *coupling errors*). Bridging errors model situations in which a given circuit value is bridged or coupled to another circuit value. This error model corresponds to many short-circuit and cross-talk fault scenarios. For example, the bridging error model is appropriate for capturing the behavior of a fabrication defect that causes a short circuit between two wires.

A higher-level error model is the *fail-stop error* model. Fail-stop errors model situations in which a component, such as a processor core or network switch, ceases to perform any function. This error model represents the impact of a wide variety of catastrophic faults. For example, chipkill memory [9, 14] is designed to tolerate fail-stop errors in DRAM chips regardless of the underlying physical fault that leads to the fail-stop behavior.

A relatively new error model is the *delay error* model, which models scenarios in which a circuit or component produces the correct value but at a time that is later than expected. Many underlying physical phenomena manifest themselves as delay errors, including progressive wear-out of transistors and the impact of process variability. Recent research called Razor [11] proposes a scheme for tolerating faults that manifest themselves as delay errors.

#### 1.4.2 Error Duration

Error models have durations that are almost always classified into the same three categories described in Section 1.2.2: transient, intermittent, and permanent. For example, an architect could consider all possible transient stuck-at errors as his or her error model.

#### 1.4.3 Number of Simultaneous Errors

A critical aspect of an error model is how many simultaneous errors it allows. Because physical faults have typically been relatively rare events, most error models consider only a single error at a time. To refine our example from the previous section, an architect could consider all possible *single* stuck-at errors as his or her error model. The possibility of multiple simultaneous errors is so unlikely that architects rarely choose to expend resources trying to tolerate these situations. Multiple-error scenarios are not only rare, but they are also far more difficult to reason about. Often, error models that

permit multiple errors force architects to consider "offsetting errors," in which the affects of one error are hidden from the error detection mechanism by another error. For example, consider a system with a parity bit that protects a word of data. If one error flips a bit in that word and another error causes the parity check circuitry to erroneously determine that the word passed the parity check, then the corrupted data word will not be detected.

There are three reasons to consider error models with multiple simultaneous errors. First, for mission-critical computers, even a vanishingly small probability of a multiple error must be considered. It is not acceptable for these computers to fail in the presence of even a highly unlikely event. Thus, these systems must be designed to tolerate these multiple-error scenarios, regardless of the associated cost. Second, as discussed in Section 1.3, there are trends leading to an increasing number of faults. At some fault rate, the probability of multiple errors becomes nonnegligible and worth expending resources to tolerate, even for non-mission-critical computers. Third, the possibility of latent errors, errors that occur but are undetected and linger in the system, can lead to subsequent multiple-error scenarios. The presence of a latent error (e.g., a bit flip in a data word that has not been accessed in a long time) can cause the next error to appear to be a multiple simultaneous error, even if the two errors occur far apart in time. This ability of latent errors to confound error models motivates architects to design systems that detect errors quickly before another error can occur and thus violate the commonly used single-error model.

#### **FAULT TOLERANCE METRICS** 1.5

In this book, we present a wide range of approaches to tolerating the faults described in the past two sections. To evaluate these fault tolerance solutions, architects devise experiments to either test hypotheses or compare their ideas to previous work. These experiments might involve prototype hardware, simulations, or analytical models.

After performing experiments, an architect would like to present his or her results using appropriate metrics. For performance, we use a variety of metrics such as instructions per cycle or transactions per minute. For fault tolerance, we have a wide variety of metrics from which to choose, and it is important to choose appropriate metrics. In this section, we present several metrics and discuss when they are appropriate.

# 1.5.1 Availability

The availability of a system at time t is the probability that the system is operating correctly at time t. For many computing applications, availability is an appropriate metric. We want to improve the availability of the processors in desktops, laptops, servers, cell phones, and many other devices. The units for availability are often the "number of nines." For example, we often refer to a system with 99.999% availability as having "five nines" of availability.

# 1.5.2 Reliability

The *reliability* of a system at time *t* is the probability that the system has been operating correctly from time zero until time *t*. Reliability is perhaps the best-known metric, and a well-known word, but it is rarely an appropriate metric for architects. Unless a system failure is catastrophic (e.g., avionics), reliability is a less useful metric than availability.

### 1.5.3 Mean Time to Failure

Mean time to failure (MTTF) is often an appropriate and useful metric. In general, we wish to extend a processor's MTTF, but we must remember that MTTF is a mean and that mean values do not fully represent probability distributions. Consider two processors,  $P_A$  and  $P_B$ , which have MTTF values of 10 and 12, respectively. At first glance, based on the MTTF metric,  $P_B$  appears preferable. However, if the *variance* of failures is much higher for  $P_B$  than for  $P_A$ , as illustrated in the example in Table 1.1, then  $P_B$  might suffer more failures in the first 3 years than  $P_A$ . If we expect our computer to have a useful lifetime of 3 years before obsolescence, then  $P_A$  is actually preferable despite its smaller MTTF. To address this limitation of MTTF, Ramachandran et al. [28] invented the nMTTF metric. If nMTTF equals a time t, for some value of n, then the probability of failure of a given processor is n/100.

# 1.5.4 Mean Time Between Failures

Mean time between failures (MTBF) is similar to MTTF, but it also considers the time to repair. MTBF is the MTTF plus the mean time to repair (MTTR). Availability is a function of MTBF, that is,

Availability =

$$\frac{\text{MTTF}}{\text{MTBF}} = \frac{\text{MTTF}}{\text{MTTF} + \text{MTTR}}$$

#### 1.5.5 Failures in Time

The failures in time (FIT) rate of a component or a system is the number of failures it incurs over one billion (10<sup>9</sup>) hours, and it is inversely proportional to MTTF. This is a somewhat odd and arbitrary metric, but it has been commonly used in the fault tolerance community. One reason for its use is that FIT rates can be added in an intuitive fashion. For example, if a system consisting of two components, A and B, fails if either component fails, then the FIT rate of the system is the FIT rate of A plus the FIT rate of B. The "raw" FIT rate of a component—the FIT rate if we do not consider failures that are architecturally masked—is often less informative than the effective FIT

| <b>TABLE 1.1:</b> Failure distributions for four chips each of P <sub>A</sub> and P <sub>B</sub> . |         |         |  |  |

|----------------------------------------------------------------------------------------------------|---------|---------|--|--|

|                                                                                                    | $P_{A}$ | $P_{B}$ |  |  |

| lifetime of chip 1                                                                                 | 9       | 2       |  |  |

| lifetime of chip 2                                                                                 | 10      | 2       |  |  |

| lifetime of chip 3                                                                                 | 10      | 21      |  |  |

| lifetime of chip 4                                                                                 | 11      | 23      |  |  |

| mean lifetime                                                                                      | 10      | 12      |  |  |

| standard deviation of lifetime                                                                     | 0.5     | 10      |  |  |

rate, which does consider such masking. We discuss how to scale the raw FIT rate next when we discuss vulnerability.

# 1.5.6 Architectural Vulnerability Factor

Architectural vulnerability factor [23] is a recently developed metric that provides insight into a structure's vulnerability to transient errors. The idea behind AVF is to classify microprocessor state as either required for architecturally correct execution (ACE state) or not (un-ACE state). For example, the program counter (PC) is almost always ACE state because a corruption of the PC almost always causes a deviation from ACE. The state of the branch predictor is always un-ACE because any state produced by a misprediction will not be architecturally visible; the processor will squash this state when it detects that the branch was mispredicted. Between these two extremes of always ACE and never ACE, there are many structures that have state that is ACE some fraction of the time. The AVF of a structure is computed as the average number of ACE bits in the structure in a given cycle divided by the total number of bits in the structure. Thus, if many ACE bits reside in a structure for a long time, that structure is highly vulnerable.

AVF can be used to scale a raw FIT rate into an effective FIT rate. The effective FIT rate of a component is its raw FIT rate multiplied by its AVF. As an extreme example, a branch predictor has an effective FIT rate of zero because all failures are architecturally masked. AVF analysis helps to identify which structures are most vulnerable to transient errors, and it helps an architect to derate how much a given structure affects a system's overall fault tolerance. Wang et al. [46] showed that AVF analysis may overestimate vulnerability in some instances and thus provides an architect with a conservative lower bound on reliability.

# 1.6 THE REST OF THIS BOOK

Fault tolerance consists of four aspects:

- Error detection (Chapter 2): A processor cannot tolerate a fault if it is unaware of it. Thus, error detection is the most important aspect of fault tolerance, and we devote the largest fraction of the book to this topic. Error detection can be performed at various granularities. For example, a localized error detection mechanism might check the correctness of an adder's output, whereas a global or *end-to-end* error detection mechanism [32] might check the correctness of an entire core.

- Error recovery (Chapter 3): When an error is detected, the processor must take action to mask its effects from the software. A key to error recovery is not making any state visible to the software until this state has been checked by the error detection mechanisms. A common approach to error recovery is for a processor to take periodic checkpoints of its architectural state and, upon error detection, reload into the processor's state a checkpoint taken before the error occurred.

- Fault diagnosis (Chapter 4): Diagnosis is the process of identifying the fault that caused an error. For transient faults, diagnosis is generally unnecessary because the processor is not going to take any action to repair the fault. However, for permanent faults, it is often desirable to determine that the fault is permanent and then to determine its location. Knowing the location of a permanent fault enables a self-repair scheme to deconfigure the faulty component. If an error detection mechanism is localized, then it also provides diagnosis, but an end-to-end error detection mechanism provides little insight into what caused the error. If diagnosis is desired in a processor that uses an end-to-end error detection mechanism, then the architect must add a diagnosis mechanism.

- Self-repair (Chapter 5): If a processor diagnoses a permanent fault, it is desirable to repair or reconfigure the processor. Self-repair may involve avoiding further use of the faulty component or reconfiguring the processor to use a spare component.

In this book, we devote one chapter to each of these aspects. Because fault-tolerant computer architecture is such a large field and we wish to keep this book focused, there are several related topics that we do not include in this book, including:

• Mechanisms for reducing vulnerability to faults: Based on AVF analysis, there has been a significant amount of research in designing processors such that they are less vulnerable to faults [47, 38]. This work is complementary to fault tolerance.

- Schemes for tolerating CMOS process variability: Process variability has recently become a significant concern [5], and there has been quite a bit of research in designing processors that tolerate its effects [20, 25, 30, 43]. If process variability manifests itself as a fault, then its impact is addressed in this book, but we do not address the situations in which process variability causes other unexpected but nonfaulty behaviors (e.g., performance degradation).

- Design validation and verification: Before fabricating and shipping chips, their designs are extensively validated to minimize the number of design bugs that escape into the field. Perfect validation would obviate the need to detect errors due to design bugs, but realistic processor designs cannot be completely validated [3].

- Fault-tolerant I/O, including disks and network controllers: This book focuses on processors and memory, but we cannot forget that there are other components in computer systems.

- Approaches for tolerating software bugs: In this book, we present techniques for tolerating hardware faults, but tolerating hardware faults provides no protection against buggy software.

We conclude in Chapter 6 with a discussion of what the future holds for fault-tolerant computer architecture. We discuss trends, challenges, and open problems in the field, as well as synergies between fault tolerance and other aspects of architecture.

#### 1.7 REFERENCES

- J. Abella, X. Vera, and A. Gonzalez. Penelope: The NBTI-Aware Processor. In *Proceedings* of the 40th Annual IEEE/ACM International Symposium on Microarchitecture, pp. 85–96, Dec. 2007.

- [2] Advanced Micro Devices. Revision Guide for AMD Athlon64 and AMD Opteron Processors. Publication 25759, Revision 3.59, Sept. 2006.

- [3] R. M. Bentley. Validating the Pentium 4 Microprocessor. In Proceedings of the International Conference on Dependable Systems and Networks, pp. 493-498, July 2001. doi:10.1109/ DSN.2001.941434

- [4] M. Blum and H. Wasserman. Reflections on the Pentium Bug. IEEE Transactions on Computers, 45(4), pp. 385-393, Apr. 1996. doi:10.1109/12.494097

- [5] S. Borkar. Designing Reliable Systems from Unreliable Components: The Challenges of Transistor Variability and Degradation. IEEE Micro, 25(6), pp. 10-16, Nov./Dec. 2005. doi:10.1109/MM.2005.110

- [6] J. R. Carter, S. Ozev, and D. J. Sorin. Circuit-Level Modeling for Concurrent Testing of Operational Defects due to Gate Oxide Breakdown. In *Proceedings of Design*, *Automation*, and Test in Europe (DATE), pp. 300–305, Mar. 2005. doi:10.1109/DATE.2005.94

- [7] J. J. Clement. Electromigration Modeling for Integrated Circuit Interconnect Reliability Analysis. *IEEE Transactions on Device and Materials Reliability*, 1(1), pp. 33–42, Mar. 2001. doi:10.1109/7298.946458

- [8] C. Constantinescu. Trends and Challenges in VLSI Circuit Reliability. *IEEE Micro*, 23(4), July–Aug. 2003. doi:10.1109/MM.2003.1225959

- [9] T. J. Dell. A White Paper on the Benefits of Chipkill-Correct ECC for PC Server Main Memory. IBM Microelectronics Division Whitepaper, Nov. 1997.

- [10] D. J. Dumin. Oxide Reliability: A Summary of Silicon Oxide Wearout, Breakdown and Reliability. World Scientific Publications, 2002.

- [11] D. Ernst et al. Razor: A Low-Power Pipeline Based on Circuit-Level Timing Speculation. In *Proceedings of the 36th Annual IEEE/ACM International Symposium on Microarchitecture*, Dec. 2003. doi:10.1109/MICRO.2003.1253179

- [12] S. Feng, S. Gupta, and S. Mahlke. Olay: Combat the Signs of Aging with Introspective Reliability Management. In *Proceedings of the Workshop on Quality-Aware Design*, June 2008.

- [13] A. H. Fischer, A. von Glasow, S. Penka, and F. Ungar. Electromigration Failure Mechanism Studies on Copper Interconnects. In *Proceedings of the 2002 IEEE Interconnect Technology Conference*, pp. 139–141, 2002. doi:10.1109/IITC.2002.1014913

- [14] IBM. Enhancing IBM Netfinity Server Reliability: IBM Chipkill Memory. IBM Whitepaper, Feb. 1999.

- [15] IBM. IBM PowerPC 750FX and 750FL RISC Microprocessor Errata List DD2.X, version 1.3, Feb. 2006.

- [16] Intel Corporation. Intel Itanium Processor Specification Update. Order Number 249720-00, May 2003.

- [17] Intel Corporation. Intel Pentium 4 Processor Specification Update. Document Number 249199-065, June 2006.

- [18] S. Krumbein. Metallic Electromigration Phenomena. *IEEE Transactions on Components*, Hybrids, and Manufacturing Technology, 11(1), pp. 5–15, Mar. 1988. doi:10.1109/33.2957

- [19] P.-C. Li and T. K. Young. Electromigration: The Time Bomb in Deep-Submicron ICs. *IEEE Spectrum*, 33(9), pp. 75–78, Sept. 1996.

- [20] X. Liang and D. Brooks. Mitigating the Impact of Process Variations on Processor Register Files and Execution Units. In *Proceedings of the 39th Annual IEEE/ACM International Symposium on Microarchitecture*, Dec. 2006.

- [21] B. P. Linder, J. H. Stathis, D. J. Frank, S. Lombardo, and A. Vayshenker. Growth and Scaling of Oxide Conduction After Breakdown. In 41st Annual IEEE International Reliability Physics Symposium Proceedings, pp. 402-405, Mar. 2003. doi:10.1109/RELPHY.2003.1197781

- [22] T. May and M. Woods. Alpha-Particle-Induced Soft Errors in Dynamic Memories. IEEE *Transactions on Electronic Devices*, 26(1), pp. 2–9, 1979.

- S. S. Mukherjee, C. Weaver, J. Emer, S. K. Reinhardt, and T. Austin. A Systematic Meth-[23] odology to Compute the Architectural Vulnerability Factors for a High-Performance Microprocessor. In Proceedings of the 36th Annual IEEE/ACM International Symposium on Microarchitecture, Dec. 2003. doi:10.1109/MICRO.2003.1253181

- S. Oussalah and F. Nebel. On the Oxide Thickness Dependence of the Time-Dependent [24] Dielectric Breakdown. In Proceedings of the IEEE Electron Devices Meeting, pp. 42-45, June 1999. doi:10.1109/HKEDM.1999.836404

- S. Ozdemir, D. Sinha, G. Memik, J. Adams, and H. Zhou. Yield-Aware Cache Architec-[25] tures. In Proceedings of the 39th Annual IEEE/ACM International Symposium on Microarchitecture, pp. 15-25, Dec. 2006.

- [26] M. D. Powell and T. N. Vijaykumar. Pipeline Damping: A Microarchitectural Technique to Reduce Inductive Noise in Supply Voltage. In Proceedings of the 30th Annual International Symposium on Computer Architecture, pp. 72-83, June 2003. doi:10.1109/ISCA.2003.1206990

- D. K. Pradhan. Fault-Tolerant Computer System Design. Prentice-Hall, Inc., Upper Saddle [27] River, NJ, 1996.

- P. Ramachandran, S. V. Adve, P. Bose, and J. A. Rivers. Metrics for Architecture-Level [28] Lifetime Reliability Analysis. In Proceedings of the International Symposium on Performance Analysis of Systems and Software, pp. 202–212, Apr. 2008.

- [29] R. Rodriguez, J. H. Stathis, and B. P. Linder. Modeling and Experimental Verification of the Effect of Gate Oxide Breakdown on CMOS Inverters. In Proceedings of the IEEE International Reliability Physics Symposium, pp. 11-16, 2003. doi:10.1109/RELPHY.2003.1197713

- B. F. Romanescu, M. E. Bauer, D. J. Sorin, and S. Ozev. Reducing the Impact of Intra-[30] Core Process Variability with Criticality-Based Resource Allocation and Prefetching. In Proceedings of the ACM International Conference on Computing Frontiers, pp. 129–138, May 2008. doi:10.1145/1366230.1366257

- S. S. Sabade and D. Walker. IDDQ Test: Will It Survive the DSM Challenge? IEEE Design [31] & Test of Computers, 19(5), pp. 8–16, Sept./Oct. 2002.

- [32] J. H. Saltzer, D. P. Reed, and D. D. Clark. End-to-End Arguments in Systems Design. ACM Transactions on Computer Systems, 2(4), pp. 277-288, Nov. 1984. doi:10.1145/357401.357402

- [33] O. Serlin. Fault-Tolerant Systems in Commercial Applications. *IEEE Computer*, 17(8), pp. 19–30, Aug. 1984.

- [34] J. Shin, V. Zyuban, P. Bose, and T. M. Pinkston. A Proactive Wearout Recovery Approach for Exploiting Microarchitectural Redundancy to Extend Cache SRAM Lifetime. In *Proceedings of the 35th Annual International Symposium on Computer Architecture*, pp. 353–362, June 2008. doi:10.1145/1394608.1382151

- [35] P. Shivakumar, M. Kistler, S. W. Keckler, D. Burger, and L. Alvisi. Modeling the Effect of Technology Trends on the Soft Error Rate of Combinational Logic. In *Proceedings of the International Conference on Dependable Systems and Networks*, June 2002. doi:10.1109/DSN.2002.1028924

- [36] D. P. Siewiorek and R. S. Swarz. *Reliable Computer Systems: Design and Evaluation*. A. K. Peters, third edition, Natick, Massachusetts, 1998.

- [37] K. Skadron, M. R. Stan, W. Huang, S. Velusamy, K. Sankaranarayanan, and D. Tarjan. Temperature-aware Microarchitecture. In *Proceedings of the 30th Annual International Symposium on Computer Architecture*, pp. 2–13, June 2003. doi:10.1145/859619.859620

- [38] N. Soundararajan, A. Parashar, and A. Sivasubramaniam. Mechanisms for Bounding Vulnerabilities of Processor Structures. In *Proceedings of the 34th Annual International Symposium on Computer Architecture*, pp. 506–515, June 2007. doi:10.1145/1250662.1250725

- [39] J. Srinivasan, S. V. Adve, P. Bose, and J. A. Rivers. The Case for Lifetime Reliability-Aware Microprocessors. In *Proceedings of the 31st Annual International Symposium on Computer Architecture*, June 2004. doi:10.1109/ISCA.2004.1310781

- [40] J. Srinivasan, S. V. Adve, P. Bose, and J. A. Rivers. The Impact of Technology Scaling on Lifetime Reliability. In *Proceedings of the International Conference on Dependable Systems and Networks*, June 2004. doi:10.1109/DSN.2004.1311888

- [41] J. H. Stathis. Physical and Predictive Models of Ultrathin Oxide Reliability in CMOS Devices and Circuits. *IEEE Transactions on Device and Materials Reliability*, 1(1), pp. 43–59, Mar. 2001. doi:10.1109/7298.946459

- [42] D. Sylvester, D. Blaauw, and E. Karl. ElastIC: An Adaptive Self-Healing Architecture for Unpredictable Silicon. *IEEE Design & Test of Computers*, 23(6), pp. 484–490, Nov./Dec. 2006.

- [43] A. Tiwari, S. R. Sarangi, and J. Torrellas. ReCycle: Pipeline Adaptation to Tolerate Process Variability. In *Proceedings of the 34th Annual International Symposium on Computer Architecture*, June 2007.

- [44] A. Tiwari and J. Torrellas. Facelift: Hiding and Slowing Down Aging in Multicores. In *Proceedings of the 41st Annual IEEE/ACM International Symposium on Microarchitecture*, pp. 129–140, Nov. 2008.

- [45] J. von Neumann. Probabilistic Logics and the Synthesis of Reliable Organisms from Unreliable Components. In C. E. Shannon and J. McCarthy, editors, *Automata Studies*, pp. 43–98. Princeton University Press, Princeton, NJ, 1956.

- [46] N. J. Wang, A. Mahesri, and S. J. Patel. Examining ACE Analysis Reliability Estimates Using Fault-Injection. In Proceedings of the 34th Annual International Symposium on Computer Architecture, June 2007. doi:10.1145/1250662.1250719

- C. Weaver, J. Emer, S. S. Mukherjee, and S. K. Reinhardt. Techniques to Reduce the Soft [47] Error Rate of a High-Performance Microprocessor. In Proceedings of the 31st Annual International Symposium on Computer Architecture, pp. 264-275, June 2004. doi:10.1109/ ISCA.2004.1310780

- [48] P. M. Wells, K. Chakraborty, and G. S. Sohi. Adapting to Intermittent Faults in Multicore Systems. In Proceedings of the Thirteenth International Conference on Architectural Support for Programming Languages and Operating Systems, Mar. 2008. doi:10.1145/1346281.1346314

- [49] J. Ziegler. Terrestrial Cosmic Rays. IBM Journal of Research and Development, 40(1), pp. 19-39, Jan. 1996.

- [50] J. Ziegler et al. IBM Experiments in Soft Fails in Computer Electronics. IBM Journal of Research and Development, 40(1), pp. 3-18, Jan. 1996.

# CHAPTER 2

# **Error Detection**

Error detection is the most important aspect of fault tolerance because a processor cannot tolerate a problem of which it is not aware. Even if the processor cannot recover from a detected error, the processor can still alert the user that an error has occurred and halt. Error detection thus provides, at the minimum, a measure of *safety*. A safe processor does not do anything incorrect. Without recovery, the processor may not be able to make forward progress, but at least it is safe. It is far preferable for a processor to do nothing than to silently fail and corrupt data.

In this chapter, as well as subsequent chapters, we divide our discussion into general concepts and domain-specific solutions. These processor domains include microprocessor cores (Section 2.2), caches and memories (Section 2.3), and multicore memory systems (Section 2.4). We divide the discussion in this fashion because the issues in each domain tend to be quite distinct.

## 2.1 GENERAL CONCEPTS

There are some fundamental concepts in error detection that we discuss now, so as to better understand the applications of these concepts to specific domains. The key to error detection is redundancy: a processor with no redundancy fundamentally cannot detect any errors. The question is not whether to use redundancy but rather what kind of redundancy should be used. The three classes of redundancy—physical (sometimes referred to as "spatial"), temporal, and information—are described in Table 2.1. All error detection schemes use one or more of these types of redundancy, and we now discuss each in more depth.

# 2.1.1 Physical Redundancy

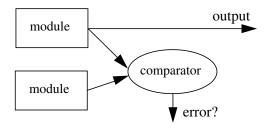

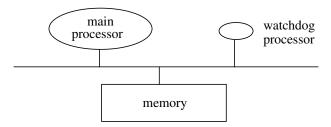

Physical (or spatial) redundancy is a commonly used approach for providing error detection. The simplest form of physical redundancy is dual modular redundancy (DMR) with a comparator, illustrated in Figure 2.1. DMR provides excellent error detection because it detects all errors except for errors due to design bugs, errors in the comparator, and unlikely combinations of simultaneous errors that just so happen to cause both modules to produce the same incorrect outputs.

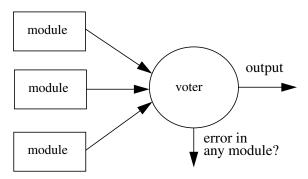

Adding an additional replica and replacing the comparator with a voter leads to the classic triple modular redundant design, shown in Figure 2.2. With triple modular redundancy (TMR),

| TABLE 2.1: The Three Types of Redundancy. |                                    |                                                                                              |  |  |

|-------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| TYPE OF REDUNDANCY                        | BASIC IDEA                         | SINGLE EXAMPLE                                                                               |  |  |

| Physical (spatial)                        | Add redundant<br>hardware          | Replicate a module and have the two replicas compare their results                           |  |  |

| Temporal                                  | Perform<br>redundant<br>operations | Run a program twice on the same<br>hardware and compare the results of<br>the two executions |  |  |

| Information                               | Add redundant bits to a datum      | Add a parity bit to a word in memory                                                         |  |  |

the output of the majority of the modules is chosen by the voter to be the output of the system. TMR offers error detection that is comparable to DMR. TMR's advantage is that, for single errors, it also provides fault diagnosis (the outvoted module has the fault) and error recovery (the system continues to run in the presence of the error). A more general physical redundancy scheme is N-modular redundancy (NMR) [86], which, for odd values of N greater than three, provides better error detection coverage, diagnosis, and recovery than TMR.

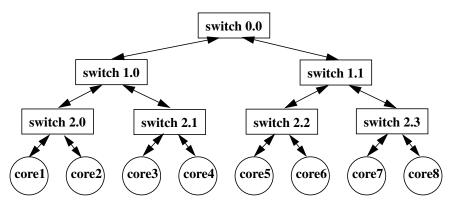

Physical redundancy can be implemented at various granularities. At a coarse grain, we can replicate an entire processor or replicate cores within a multicore processor. At a finer grain, we can replicate an ALU or a register. Finer granularity provides finer diagnosis, but it also increases the relative overhead of the voter. Taken to an absurdly fine extreme, using TMR at the granularity of a single NAND gate would create a scenario in which the voter was larger than the three modules.

Physical redundancy does not have to be homogeneous. That is, the redundant hardware does not have to be identical to the original hardware. Heterogeneity, also called "design diversity" [6], can serve two purposes.

FIGURE 2.1: Dual modular redundancy.

FIGURE 2.2: Triple modular redundancy.

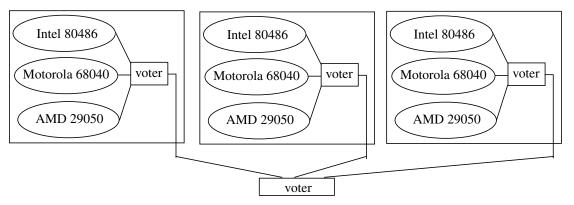

First, it enables detection of errors due to design bugs. The Boeing 777 [93] uses heterogeneous "triple-triple" modular redundancy, as illustrated in Figure 2.3. This design uses heterogeneous processors within each unit and thus a design bug in any of the processors will be detected (and corrected) by the other two processors in the unit. The second benefit of heterogeneity is the ability to reduce the cost of the redundant hardware, as compared to homogeneous redundancy. In many situations, it is easier to check that an operation is performed correctly than to perform the operation; in these situations, a heterogeneous checker can be smaller and cheaper than the unit it is checking. An extreme example of heterogeneous hardware redundancy is a watchdog timer [42]. A watchdog timer is a piece of hardware that monitors other hardware for signs of liveness. For example, a processor's watchdog timer might track memory requests on the bus. If no requests have been observed for an extremely long time that exceeds a predefined threshold, then the watchdog timer reports that an error has occurred. Checking a processor's liveness is far simpler than performing

FIGURE 2.3: Boeing 777's triple TMR [93].

all of the processor's operations, and a watchdog timer can thus be far cheaper than a redundant processor.

The primary costs of physical redundancy are the hardware cost and power and energy consumption. For example, compared to an unprotected system, a system with TMR uses more than three times as much hardware (two redundant modules and a voter) and a corresponding extra amount of power and energy. For mission-critical systems that require the error detection capability of NMR, these costs may be unavoidable, but these costs are rarely acceptable for commodity processors. In particular, as modern processors try to extract as much performance as possible for a given energy and power budget, NMR's power and energy costs are almost certainly impractical. Also, when using NMR, a designer must remember that N times as much hardware is susceptible to N times as many errors, if we assume a constant error rate per unit of hardware.

# 2.1.2 Temporal Redundancy

In its most basic form, temporal redundancy requires a unit to perform an operation twice (or more times, in theory, but we only consider two iterations here), one after the other, and then compare the results. Thus, the total time is doubled, ignoring the latency to compare the results, and the performance of the unit is halved. Unlike with physical redundancy, there is no extra hardware or power cost (once again ignoring the comparator). However, as with DMR, the active energy consumption is doubled because twice as much work is performed.

Because of temporal redundancy's steep performance cost, many schemes use pipelining to hide the latency of the redundant operation. As one example, consider a fully pipelined unit, such as a multiplier. Assume that a multiplication takes X cycles to complete. If we begin the initial computation on cycle C, we can begin the redundant computation on cycle C+1. The latency of the checked multiplication is only increased by one cycle; instead of completing on cycle C+X, it now completes on cycle C+X+1. This form of temporal redundancy reduces the latency penalty significantly, but it still has a throughput penalty because the multiplier can perform only half as many unique (nonredundant) multiplications per unit of time. This form of temporal redundancy does not address the energy penalty at all; it still uses twice as much active energy as a nonredundant unit.

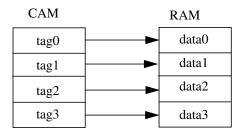

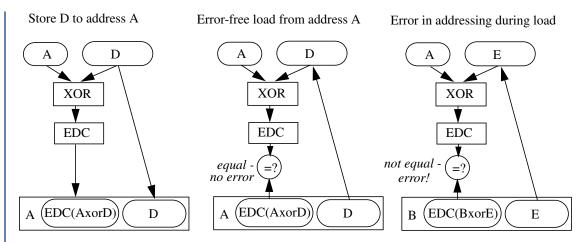

# 2.1.3 Information Redundancy

The basic idea behind information redundancy is to add redundant bits to a datum to detect when it has been affected by an error. An *error-detecting code* (*EDC*) maps a set of  $2^k$  k-bit datawords to a set of  $2^k$  n-bit "codewords," where n > k. The key idea is to map the datawords to codewords such that the codewords are as "far apart" from each other as possible in the n-dimensional codeword space.

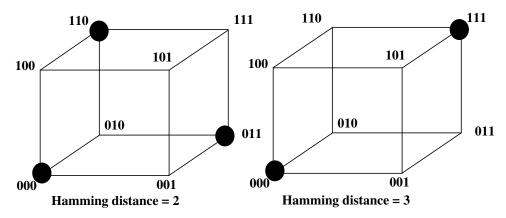

The distance between any two codewords, called the Hamming distance (HD), is the number of bit positions in which they differ. For example, 01110 and 11010 differ in two bit positions.

The HD of an EDC is the minimum HD between any two codewords, and the EDC's HD is what determines how many single bit-flip errors it can detect in a single codeword. The two examples in Figure 2.4 pictorially illustrate two EDCs, one with an HD of two and the other with three. In the HD=2 example, we observe that, for any legal codeword, an error in any one of its bits will transform the codeword into an illegal word in the codeword space. For example, a single-bit error might transform 011 into 111, 001, or 010; none of these three words is a legal codeword. Thus, a single-bit error will always be detected because it will lead to an illegal word. A double-bit error might transform 011 into 000, which is also a legal codeword and would thus be undetected. In the HD=3 example, for either legal codeword, an error in any one or two of its bits will transform the codeword into an illegal word. Thus, a single-bit or double-bit error will always be detected. More generally, an EDC can detect errors in up to HD-1 bit positions.

The simplest and most common EDC is parity. Parity adds one parity bit to a dataword to convert it into a codeword. For even (odd) parity, the parity bit is added such that the total number of ones in the codeword is even (odd). Parity is an HD=2 EDC that can thus detect single-bit errors. Parity is popular because it is simple and inexpensive to implement, and it provides decent error detection coverage.

More sophisticated codes with larger HDs can detect more errors, and many of these codes can also correct errors. An error-correcting code (ECC) adds enough redundant bits to provide correction. For example, the HD=3 code in Figure 2.4 can correct single-bit errors. Consider the three possible single-bit errors in the codeword 000: 001, 010, and 100. All three of these codewords are

FIGURE 2.4: Hamming distance examples. Black circles denote legal codewords. Vertices without black circles correspond to illegal words in the codeword space.

closer to 000 than they are to the next nearest codeword, 111. Thus, the code would correct the error by interpreting 001, 010, or 100 as being the codeword 000. An ECC can correct errors in up to (HD-1)/2 bit positions. In Figure 2.5, we illustrate a more efficient HD=3 ECC known as a *Hamming* (7,4) code because codewords are 7 bits and datawords are 4 bits. This ECC, like the simpler but less efficient HD=3 code in Figure 2.4, can also correct a single-bit error. The Hamming (7,4) code has an overhead that is 3 bits per 4-bit dataword compared to the simpler code that adds 2 bits per 1-bit dataword.

Error codes are often classified based on their detection and correction abilities. A common classification is SECDED, which stands for "single-error correcting (SEC) and double-error detecting (DED)" and has an HD of 4. Note that the HD=3 example in Figure 2.4 can either correct single errors or detect single or double errors, but it cannot do both. For example, if this code is to

Creating a codeword. Given a 4-bit dataword  $\underline{D} = [d1 \ d2 \ d3 \ d4]$ , we construct a 7-bit codeword  $\underline{C}$  by computing three overlapping parity bits:

p1 = d1 xor d2 xor d4

p2 = d1 xor d3 xor d4

p4 = d2 xor d3 xor d4

The 7-bit codeword  $\underline{C} = [p1 \ p2 \ d1 \ p4 \ d2 \ d3 \ d4].$

Correcting errors in a possibly corrupted codeword. Given a 7-bit word  $\underline{R}$ , we check it by multiplying it with the parity check matrix matrix  $\underline{H}$  below:

| p1 | p2 | d1 | p4 | d2 | d3 | d4 |

|----|----|----|----|----|----|----|

| 1  | 0  | 1  | 0  | 1  | 0  | 1  |

| 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| 0  | 0  | 0  | 1  | 1  | 1  | 1  |

If <u>R</u> is a valid codeword, then <u>HR=0</u>, and no error correction is required.

Else, if  $\underline{R}$  is a corrupted codeword, then  $\underline{HR} = \underline{S}$ , where the 3-bit  $\underline{S}$  indicates the error's location.

Example 1:  $\underline{\mathbf{R}} = [0100101]$ .  $\underline{\mathbf{HC}} = [0\ 0\ 0] = \underline{\mathbf{0}} -->$  no error

Example 2:  $\underline{\mathbf{R}} = [01\mathbf{1}0101]$  (error in bit position 3).  $\underline{\mathbf{HC}} = [1\ 1\ 0]$  --> we read the syndrome backwards to determine that the error location is in bit position 011 = 3

FIGURE 2.5: Hamming (7,4) code.

be used for SEC instead of DED, then a 001 would be corrected to be 000 instead of considering the possibility that a double-error had turned a 111 into 001. SECDED codes are commonly used for a variety of dataword sizes.

In Table 2.2, we show the relationship between dataword size and codeword size, for dataword sizes ranging from 8 to 256 bits.

We summarize the error detection and correction capabilities of error codes in Table 2.3. In this table, we include the capability to correct erasures. An erasure is a bit that is unreadable; the logic cannot tell if it is a 0 or a 1. Erasures are common in network communications, and they also occur in storage structures when a portion of the storage (e.g., a DRAM chip or a disk in a RAID array) is unresponsive because of a catastrophic failure. Correcting an erasure is easier than correcting an error because, with an erasure, we know the location of the erased bit. For example, consider an 8-bit dataword with a single parity bit. This parity bit can be used to detect a single error or to correct a single erasure, but it is insufficient to correct a single error.

There exist many error codes, and discussing them in depth is beyond the scope of this book. For a more complete treatment of the topic, we refer the interested reader to Wakerly's [88] excellent book on EDCs.

#### 2.1.4 The End-to-End Argument

We can apply redundancy to detect errors at many different levels in the system—at the transistor, gate, cache block, core, and so on. A question for a computer architect is what level or levels are appropriate. Saltzer et al. [64] argued for "end-to-end" error detection in which we strive to

| TABLE 2.2: SECDED Codes for Various Dataword Sizes. |                                 |                                |  |  |

|-----------------------------------------------------|---------------------------------|--------------------------------|--|--|

| DATAWORD<br>SIZE (BITS)                             | MINIMUM CODEWORD<br>SIZE (BITS) | SECDED STORAGE<br>OVERHEAD (%) |  |  |

| 8                                                   | 13                              | 62.5                           |  |  |

| 16                                                  | 22                              | 37.5                           |  |  |

| 32                                                  | 39                              | 21.9                           |  |  |

| 64                                                  | 72                              | 12.5                           |  |  |

| 128                                                 | 137                             | 7.0                            |  |  |

| 256                                                 | 266                             | 3.9                            |  |  |

|                    | TABLE 2.3: Summary of EDC and ECC Capabilities. |                       |                             |  |  |

|--------------------|-------------------------------------------------|-----------------------|-----------------------------|--|--|

| ERRORS<br>DETECTED | ERRORS<br>CORRECTED                             | ERASURES<br>CORRECTED | MINIMUM HAMMING<br>DISTANCE |  |  |

| D                  | 0                                               | 0                     | D+1                         |  |  |

| 0                  | 0                                               | E                     | E+1                         |  |  |

| 0                  | С                                               | 0                     | 2C+1                        |  |  |

| D                  | С                                               | 0                     | 2C+D+1                      |  |  |

| D                  | 0                                               | E                     | D+E+1                       |  |  |

| 0                  | С                                               | E                     | 2C+E+1                      |  |  |

| D                  | С                                               | E                     | 2C+D+E+1                    |  |  |

perform error detection at the "ends" or the highest level possible. Instead of adding hardware to immediately detect errors as soon as they occur, the end-to-end argument suggests that we should wait to detect errors until they manifest themselves as anomalous higher-level behaviors. For example, instead of detecting that a bit flipped, we would prefer to wait until that bit flip resulted in an erroneous instruction result or a program crash. By checking at a higher level, we can reduce the hardware costs and reduce the number of false positives (detected errors that have no impact on the core's behavior). Furthermore, we *have* to check at the ends anyway because only at the ends does the system have sufficient semantic knowledge to detect certain types of errors.

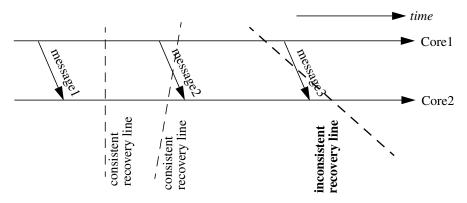

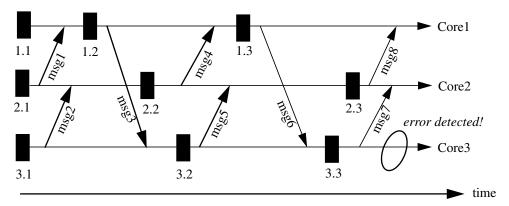

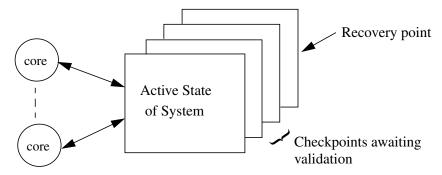

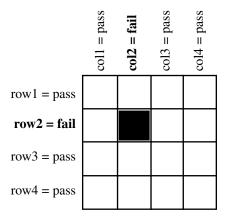

Relying only on end-to-end error detection has three primary drawbacks. First, detecting a high-level error like a program crash provides little diagnostic information. If the crash is due to a permanent fault, it would be beneficial to have some idea of where the fault is that caused the crash, or even that the crash was due to a physical fault and not a software bug. If only end-to-end error detection is used, then additional diagnostic mechanisms may be necessary.