Hammad M. Cheema Reza Mahmoudi Arthur H.M. van Roermund

# 60-GHz CMOS Phase-Locked Loops

60-GHz CMOS Phase-Locked Loops

Hammad M. Cheema • Reza Mahmoudi • Arthur H. M. van Roermund

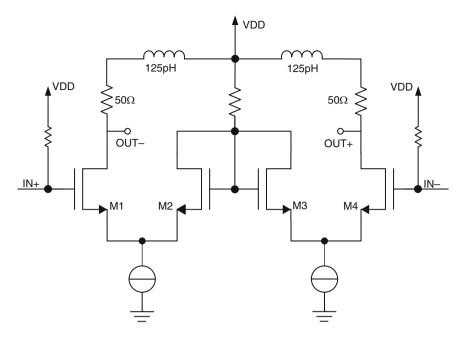

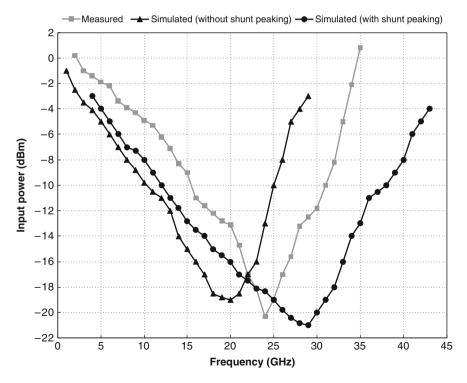

## 60-GHz CMOS Phase-Locked Loops

Hammad M. Cheema Eindhoven University of Technology Electrical Engineering Den Dolech 2 5600 MB Eindhoven Netherlands h.m.cheema@tue.nl

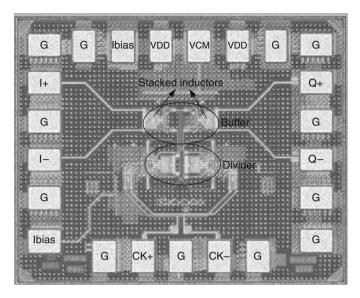

Dr. Arthur H. M. van Roermund Eindhoven University of Technology Dept. Electrical Engineering Eindhoven Netherlands a.h.m.v.roermund@tue.nl Reza Mahmoudi Eindhoven University of Technology Electrical Engineering Den Dolech 2 5600 MB Eindhoven Netherlands r.mahmoudi@tue.nl

ISBN 978-90-481-9279-3 e-ISBN 978-90-481-9280-9 DOI 10.1007/978-90-481-9280-9 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: 2010930220

© Springer Science+Business Media B.V. 2010

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: eStudio Calamar S.L.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Contents

| 1 | Introduction                                       | 1   |

|---|----------------------------------------------------|-----|

| 2 | Synthesizer System Architecture                    | 11  |

|   | 2.1 IEEE 802.15.3c Channelization                  | 13  |

|   | 2.2 60 GHz Frequency Conversion Techniques         | 14  |

|   | 2.3 Proposed PLL Architecture: Flexible, Reusable, |     |

|   | Multi-frequency                                    | 17  |

|   | 2.3.1 Utilization in WiComm Project                | 18  |

|   | 2.4 System Analysis and Design                     | 18  |

|   | 2.4.1 Phase-Lock Loop Basics                       | 19  |

|   | 2.4.2 Frequency Planning                           | 21  |

|   | 2.4.3 Synthesizer Parameters                       | 22  |

|   | 2.5 System Simulations                             | 28  |

|   | 2.6 Target Specifications                          | 32  |

|   | 2.7 Summary                                        | 33  |

| _ |                                                    | ~ ~ |

| 3 | Layout and Measurements at mm-Wave Frequencies     | 35  |

|   | 3.1 Layout Problems and Solutions                  | 36  |

|   | 3.1.1 Impact of Parasitics                         | 37  |

|   | 3.1.2 Mismatch Due to Layout Asymmetry             |     |

|   | and Device Orientation                             | 41  |

|   | 3.1.3 Substrate Losses                             | 42  |

|   | 3.1.4 Cross Talk Shielding and Grounding           | 44  |

|   | 3.2 Measurement Setups                             | 48  |

|   | 3.2.1 Dedicated Instrumentation                    | 49  |

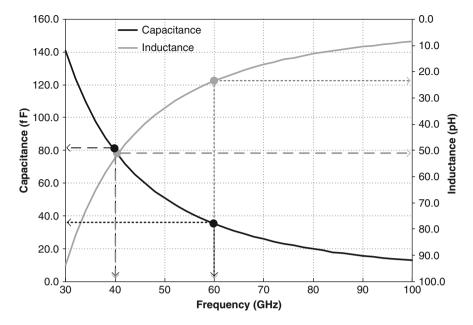

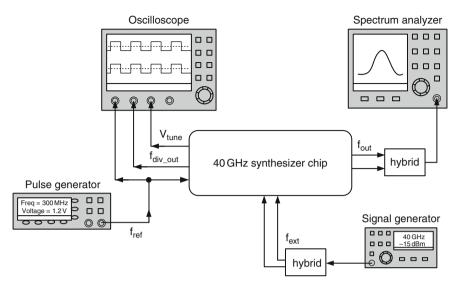

|   | 3.2.2 Calibration and De-embedding                 | 51  |

|   | 3.2.3 Stability and Repeatability                  | 54  |

|   | 3.3 Conclusions                                    | 55  |

| 4  | Design of High Frequency Components                         | 57  |

|----|-------------------------------------------------------------|-----|

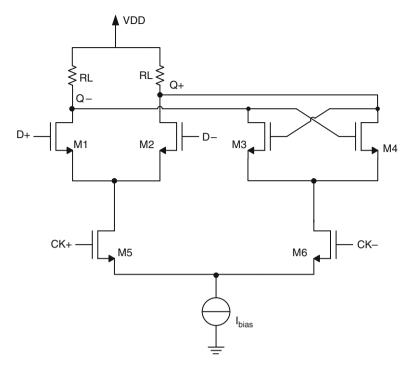

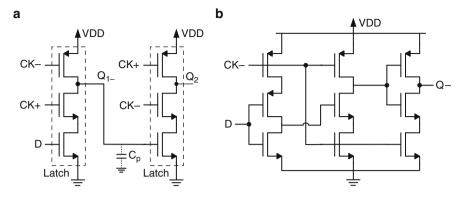

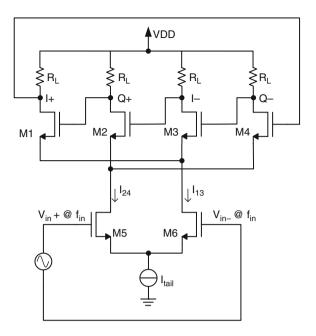

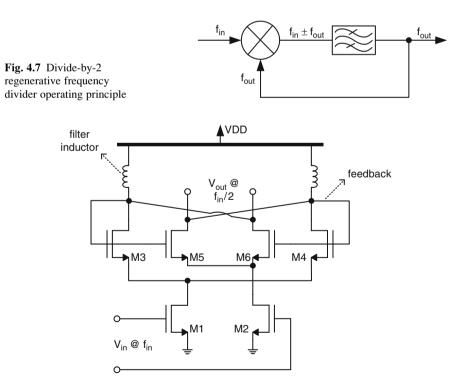

|    | 4.1 Prescaler                                               |     |

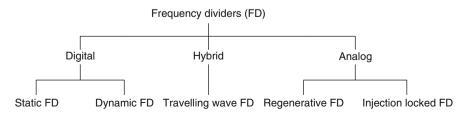

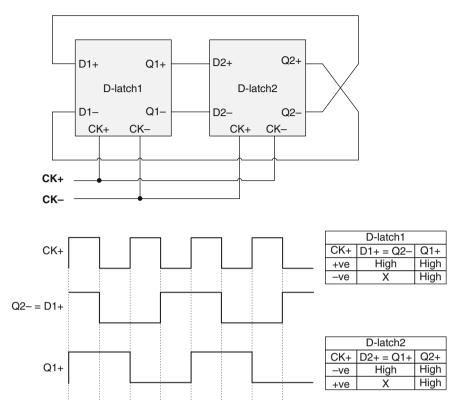

|    | 4.1.1 Overview and Comparison of Prescaler Architectures    | 60  |

|    | 4.1.2 35 GHz Static Frequency Divider                       | 69  |

|    | 4.1.3 40 GHz Divide-by-2 ILFD                               | 78  |

|    | 4.1.4 60 GHz Divide-by-3 ILFD                               |     |

|    | 4.1.5 Monolithic Transformer Design and Measurement         |     |

|    | 4.1.6 Dual-Mode (Divide-by-2 and Divide-by-3) ILFD          |     |

|    | 4.1.7 ILFD figure-of-Merit (FOM)                            | 104 |

|    | 4.1.8 Summary                                               | 106 |

|    | 4.2 Voltage Controlled Oscillator                           | 106 |

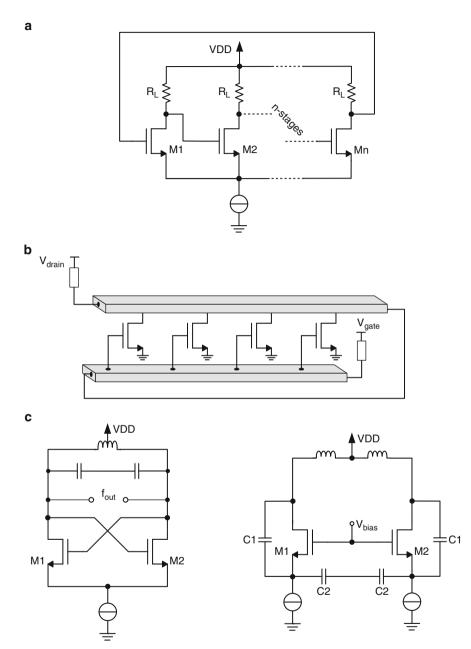

|    | 4.2.1 Overview of VCO Architectures                         | 107 |

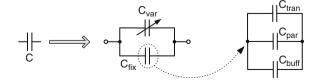

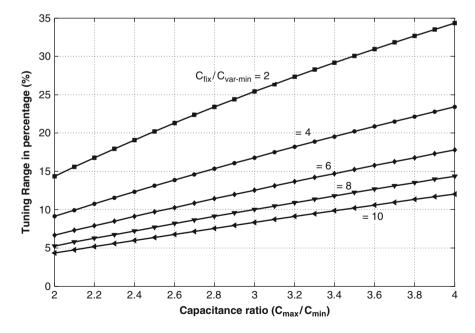

|    | 4.2.2 Theoretical Analysis of LC-VCOs                       | 111 |

|    | 4.2.3 40 GHz LC VCO                                         | 115 |

|    | 4.2.4 60 GHz Actively Coupled I-Q VCO                       | 123 |

|    | 4.2.5 60 GHz Transformer Coupled I-Q VCO                    | 129 |

|    | 4.2.6 Dual-Band VCO for 40 and 60 GHz                       | 137 |

|    | 4.3 Synthesizer Front-Ends                                  | 140 |

|    | 4.3.1 40 GHz VCO and Divide-by-2 ILFD                       | 141 |

|    | 4.3.2 60 GHz VCO and Divide-by-3 ILFD                       | 146 |

|    | 4.4 Conclusions                                             | 148 |

|    |                                                             |     |

| 5  | Design of Low Frequency Components                          | 151 |

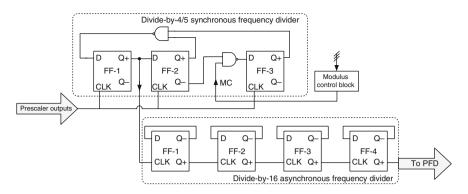

|    | 5.1 Feedback Division                                       | 152 |

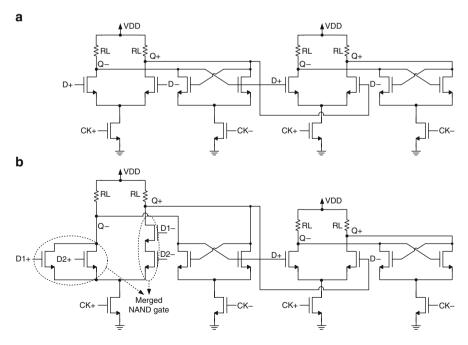

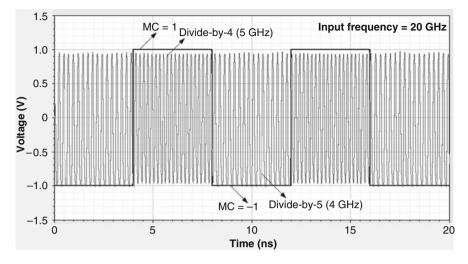

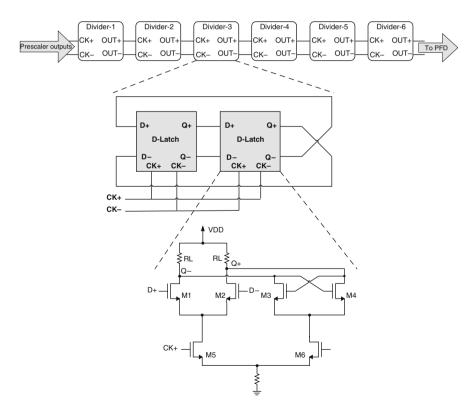

|    | 5.1.1 CML Based Divider Chain                               | 152 |

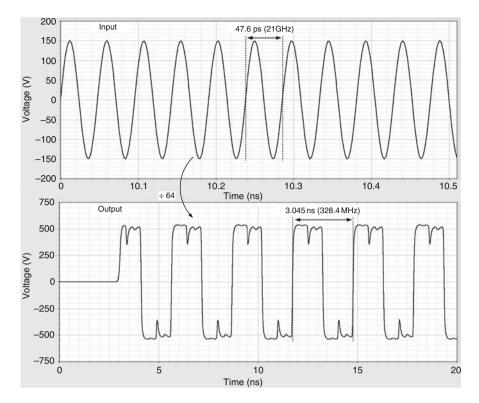

|    | 5.1.2 Mixer Based Division                                  | 157 |

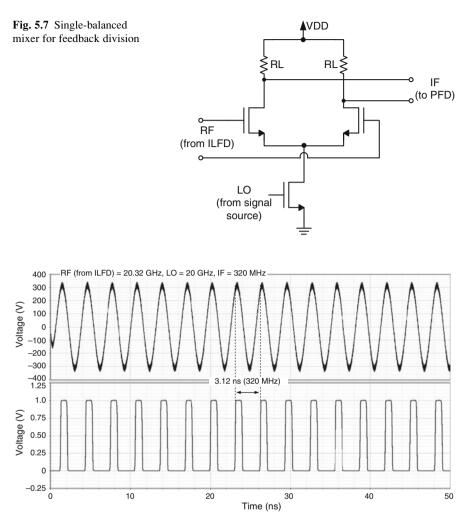

|    | 5.2 Phase-Frequency Detector, Charge-Pump and Loop Filter   | 160 |

|    | 5.3 Conclusions                                             | 164 |

|    |                                                             |     |

| 6  | Synthesizer Integration                                     | 165 |

|    | 6.1 Synthesizer for 60 GHz Sliding-IF Frequency Conversion  | 166 |

|    | 6.1.1 Comparison to Target Specifications                   | 174 |

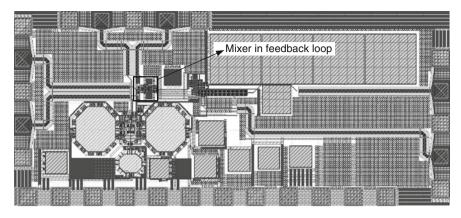

|    | 6.2 Synthesizer with Down-Conversion Mixer in Feedback Loop | 175 |

|    | 6.3 Dual-Mode Synthesizer                                   | 177 |

|    | 6.4 Conclusions                                             | 180 |

|    |                                                             |     |

| 7  | Conclusions                                                 | 183 |

|    |                                                             |     |

| A  | ppendix                                                     | 185 |

|    | Appendix A                                                  | 185 |

|    | A Travelling Wave Divider Simulation Results                | 185 |

|    | Appendix B                                                  | 186 |

|    | B LC-VCOs Theory                                            | 186 |

|    | •                                                           |     |

| Re | eferences                                                   | 191 |

## Acronyms

| AMOS  | Accumulation metal oxide semiconductor    |  |  |

|-------|-------------------------------------------|--|--|

| CMOS  | Complementary metal oxide semiconductor   |  |  |

| CP    | Charge pump                               |  |  |

| DCM   | Distributed capacitance model             |  |  |

| DM-FD | Dual modulus frequency divider            |  |  |

| DSP   | Digital signal processing                 |  |  |

| DUT   | Device under test                         |  |  |

| DVCO  | Distributed voltage controlled oscillator |  |  |

| EMF   | Electromotive force                       |  |  |

| FCC   | Federal Communication Commission          |  |  |

| FF    | Flip-flop                                 |  |  |

| FOM   | Figure of merit                           |  |  |

| FSR   | Frequency of self resonance               |  |  |

| FTR   | Frequency tuning range                    |  |  |

| GaAs  | Galium arsenide                           |  |  |

| HBT   | Heterojunction bipolar transistor         |  |  |

| HDMI  | High definition multimedia interface      |  |  |

| HDTV  | High definition television                |  |  |

| IC    | Integrated circuit                        |  |  |

| IF    | Intermediate frequency                    |  |  |

| ILFD  | Injection locked frequency divider        |  |  |

| ISF   | Impulse sensitivity function              |  |  |

| ISS   | Impedance standard substrates             |  |  |

| LPF   | Low pass filter                           |  |  |

| LO    | Local oscillator                          |  |  |

| MC    | Modulus control                           |  |  |

| MCML  | MOS current mode logic                    |  |  |

| MIM   | Metal-insulator-metal                     |  |  |

| PFD   | Phase frequency detector                  |  |  |

| PDA   | Personal digital assistant                |  |  |

|       | 0                                         |  |  |

| PLL  | Phase-locked loop                   |

|------|-------------------------------------|

| PM   | Phase margin                        |

| PMP  | Portable media player               |

| PN   | Phase noise                         |

| Q    | Quality factor                      |

| RF   | Radio frequency                     |

| RFD  | Regenerative frequency divider      |

| RFIC | Radio frequency integrated circuits |

| SA   | Spectrum analyzer                   |

| SCL  | Source coupled logic                |

| SFD  | Static frequency divider            |

| SG   | Signal generator                    |

| SiGe | Silicon germanium                   |

| SoA  | Silicon on anything                 |

| SOI  | Silicon on insulator                |

| TSPC | True single phase clocking          |

| TWD  | Travelling wave divider             |

| UWB  | Ultra wide-band                     |

| VCO  | Voltage controlled oscillator       |

| VNA  | Vector network analyzer             |

| WLAN | Wireless local area networks        |

| WPAN | Wireless personal area networks     |

|      |                                     |

## Chapter 1 Introduction

**Abstract** This chapter lays the foundation for the work presented in latter chapters. The potential of 60 GHz frequency bands for high data rate wireless transfer is discussed and promising applications are enlisted. Furthermore, the challenges related to 60 GHz IC design are presented and the chapter concludes with an outline of the book.

**Keywords** Wireless communication  $\cdot$  60 GHz  $\cdot$  Millimeter wave integrated circuit design  $\cdot$  Phase-locked loop  $\cdot$  CMOS

Communication technology has revolutionized our way of living over the last century. Since Marconi's transatlantic wireless experiment in 1901, there has been tremendous growth in wireless communication evolving from spark-gap telegraphy to today's mobile phones equipped with Internet access and multimedia capabilities. The omnipresence of wireless communication can be observed in widespread use of cellular telephony, short-range communication through wireless local area networks and personal area networks, wireless sensors and many others.

The frequency spectrum from 1 to 6 GHz accommodates the vast majority of current wireless standards and applications. Coupled with the availability of low cost radio frequency (RF) components and mature integrated circuit (IC) technologies, rapid expansion and implementation of these systems is witnessed. The downside of this expansion is the resulting scarcity of available bandwidth and allowable transmit powers. In addition, stringent limitations on spectrum and energy emissions have been enforced by regulatory bodies to avoid interference between different wireless systems.

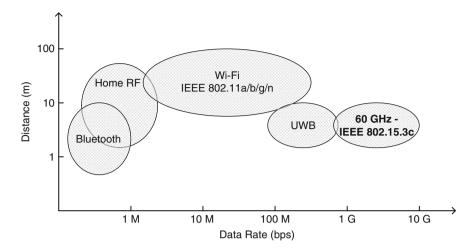

At the same time, driven by customer demands, the last 2 decades have also experienced unprecedented progress in wireless portable devices capable of supporting multi-standard applications. The allure of "being connected" at anytime anywhere and desire for untethered access to information and entertainment "on the go" has set the ever increasing demand for higher data rates. As shown in Fig. 1.1, contemporary systems are capable of supporting light or moderate levels of

Fig. 1.1 Data rate and distance comparison for different WPAN and WLAN technologies

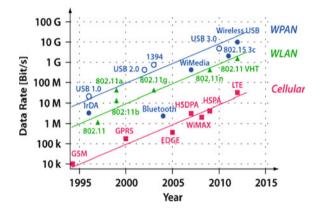

Fig. 1.2 Increasing data rate trend according to Edholm's law [2]

wireless data traffic, as in Bluetooth and wireless local area networks (WLANs). However, they are unable to deliver data rates comparable to wired standards like gigabit Ethernet and high-definition multimedia interface (HDMI) [1]. Furthermore, as predicted by Edholm's law [2], the required data rates (and associated bandwidths) have doubled every 18 months over the last decade. This trend is shown in Fig. 1.2 for cellular, wireless local area networks and wireless personal area networks for last 15 years.

The current standards and applications operating between 1 and 6 GHz have their market for long distance communication; however, in order to address the spectrum congestion and data rate issues mentioned above, new solutions have to be explored. As stated by Shannon [3], the maximum available capacity of a communication system increases linearly with channel bandwidth and logarithmically with the signal-to-noise ratio. Therefore, the obvious choice is to look upwards in the frequency spectrum where more bandwidth could be available.

An intermediate solution offered was the introduction of ultra-wide band (UWB) in 2002 by the Federal Communications Commission (FCC). It offers the frequency spectrum from 3.1 to 10.6 GHz and a minimum required bandwidth of 500 MHz for its applications. Although UWB partially solves the bandwidth issue and can potentially support high data rates, there are some limitations hindering its popularity. Firstly, international coordination is difficult to achieve among major countries and IEEE standards are not accepted worldwide. Secondly, as UWB is an overlay system over the existing 2.4 and 5 GHz unlicensed bands used for already deployed WLANs, the inter-system interference is a major concern. In order to safeguard the existing wireless systems in different regions, local regulatory bodies have defined their own requirements for UWB making world-wide harmonization of UWB almost impossible. Furthermore, to avoid interference, the allowed transmit power is low giving rise to reliability concerns. Thirdly, current multi-band orthogonal frequency division multiplexing (MB-OFDM) based UWB systems can provide data rates uptil 480 Mbps which can only support compressed video. Uncompressed high-definition television (HDTV) can easily require 2 Gbps or more data rate, which although possible by enhancing MB-OFDM UWB, increases the complexity, cost and power consumption many folds. Lastly, variation of the received signal strength over the entire UWB spectrum poses sensitivity problems for the receiver [4, 5].

The above constraints of interference, transmit power and low data rate motivated the exploration of completely unoccupied frequency band in the millimeter wave (mm-wave) regime and 60 GHz appeared as one of the promising candidates for the purpose.

In 2001, spurred by the increasing demand of high data rate applications and limitations of current wireless technologies, a 7 GHz contiguous bandwidth was allocated world-wide by the FCC. There was an immediate interest, both in academia and industry, to investigate the opportunities and possibilities using this large chunk of bandwidth. The fact that this band was unlicensed further helped in triggering the research effort. The regional regulatory bodies allocated local frequency bands with slight shift and defined the maximum effective isotropic radiated power (EIRP). Table 1.1 lists these two parameters for different regions.

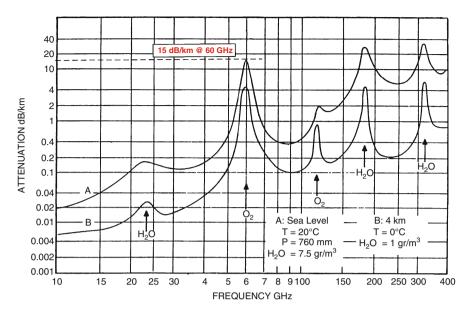

The maximum allowed EIRP at 60 GHz is much higher than other existing WLANs and WPANs. This is essential to overcome the higher space path loss (according to classic Friis formula) and oxygen absorption of 10–15 dB/km as shown in Fig. 1.3 [6]. These two loss mechanisms dictate the use of 60 GHz for short range multi-gigabit per second transmission. The attenuation also means that

| Table 1.1 Regional spectrum                   | Region     | Frequency band (GHz) | Max. EIRP (dBm) |

|-----------------------------------------------|------------|----------------------|-----------------|

| allocation and emission<br>power requirements | Europe     | 59–66                | 57              |

| power requirements                            | Canada/USA | 57–64                | 43              |

|                                               | Korea      | 57–64                | 43              |

|                                               | Japan      | 59–66                | 57              |

|                                               | Australia  | 59.4-62.9            | 51.8            |

Fig. 1.3 Gaseous absorption at 60 GHz [6]

the system provides inherent security, as radiation from one particular 60 GHz radio link is quickly reduced to a level that does not interfere with other 60 GHz links operating in the same vicinity. Furthermore, this reduction enables the ability for more 60 GHz radio-enabled devices to successfully operate within one location.

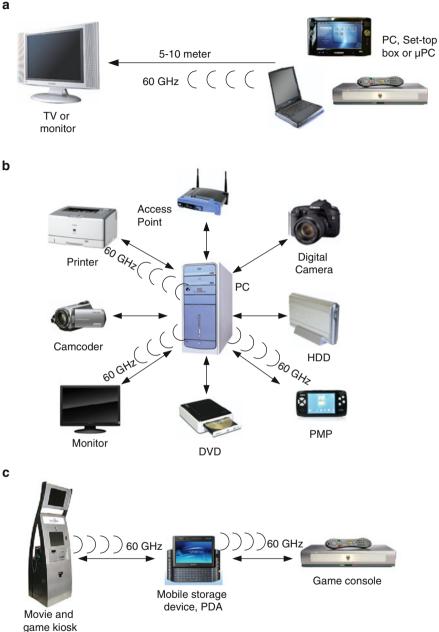

Using the 60 GHz band for high data rate and indoor wireless transmission, a multitude of potential applications can be envisioned. The high definition multimedia interface (HDMI) cable could be replaced by a wireless system, transmitting uncompressed video streams from DVD players, set-top boxes, PC's to a TV or monitor. Current wireless HDMI products utilize the 2.5 and 5 GHz unlicensed spectrum where bandwidth is limited. As a result, these systems implement either lossy or lossless compression, significantly adding component and design cost, digital processing complexity and product size. Typical distance between these gadgets is 5–10 m and this communication can be point-to-point or point-to-multipoint. Depending on the resolution and pixels per line, the data rate required can vary from several hundred megabit per second (Mbps) to a few gigabit per second (Gbps). For instance, a typical high definition television (HDTV) offers a resolution of  $1,920 \times 1,080$  with a refresh rate of 60 Hz. Assum-ing RGB video format with 8 b per channel per pixel, the required data rate is approximately 3 Gbps [1]. The future HDTV generation is expected to offer higher refresh rates as well as higher number of bits per channel scaling the required data rate beyond 5 Gbps. Therefore, transmitting HDTV transmission using 60 GHz remains an attractive test-case in the research field. Similarly, video and audio streams from personal digital assistant (PDA), portable media player (PMP) and laptops can also be transferred wirelessly to a display device.

In an office or home environment, 60 GHz radio links can essentially replace the clutter of cables of standards like USB, IEEE 1394, gigabit Ethernet and multimedia delivery. A PC can "talk" to all the external peripherals including printers, DVD writers, camcorders, digital cameras, external hard-disks and so forth. Wireless gigabit Ethernet and wireless ad hoc networks using 60 GHz are attractive applications for a conference room or library environment. A commercial application, particularly interesting for youth, is the so-called "Kiosk file downloading" in which users can download movies, games etc from a kiosk placed at locations like airports, railway-stations, market places and so on. These application examples are summarized in Fig. 1.4.

In addition to home and office, 60 GHz vehicular applications are also gaining much attention. They can be partitioned in three classes namely [4, 5]:

- Intra-vehicle wireless networks can be considered as a subset of WPANs that exist completely within a vehicle. The possibility of broadband communication within an automobile or aircraft by removing wired connections is desirable for manufacturers. The 60 GHz band is especially suited for intra-vehicle applications due to the containment within the vehicle and reduced ability to interfere with other vehicular networks.

- Inter-vehicle wireless networks are different from the intra-vehicle networks due to the outdoor propagation environment in the former. Applications like delivery of traffic information and range extension of mobile broadband networks are possible using inter-vehicle networks at 60 GHz.

- Vehicular radar, the last class of vehicular applications, has been deployed at millimeter-wave frequencies other than 60 GHz before; however, adaptive cruise control and automotive localization using the 60 GHz band have attracted interest in recent times.

Despite many advantages and attractive applications of short range gigabit per second wireless transmission at 60 GHz, a number of technical challenges related to design and performance need to be addressed. These can be broadly categorized into channel propagation issues, antenna technology, modulation schemes and integrated circuit technology and design.

In the last category, the choice of IC technology depends on the implementation aspects and system requirements. The former is related to the issues such as power consumption, efficiency, linearity and so on, while the latter is related to the transmission rate, cost and size, modulation etc. There are three competing IC technologies at mm-wave namely:

- Group III-V, such as Gallium Arsenide (GaAs) and Indium Phospide (InP). This technology offers fast, high gain and low noise circuits but suffers from poor integration and expensive implementation.

- Silicon germanium (SiGe) technology, such as heterojunction bipolar transistor (HBT) and BiCMOS are cheaper alternatives of GaAs and offer comparable performance.

Fig. 1.4 Potential 60 GHz applications: point-to-point HDTV transmission (a), communication between a PC and different peripherals (b) and kiosk file downloading (c)

• Silicon technology, such as CMOS and BiCMOS. As size and cost are key factors for mass market production and deployment, CMOS technology appears to be the leading candidate as it offers high level of integration and is economical as compared to other alternatives. The downside of using CMOS is performance degradation due to low gain, linearity constraints, poor noise, low transition frequency ( $f_T$ ) etc. However, the recent advances in CMOS technology, like silicon-on-insulator (SOI) and silicon-on-anything (SOA), coupled with continuous down-scaling to sub-nanometer technologies is facilitating the implementation of integrated circuits at 60 GHz. Furthermore, high speed digital signal processing (DSP) capabilities required for processing gigabit per second data is also possible using CMOS.

In order to circumvent the abovementioned performance limitations of CMOS, especially for phase-locked loops (PLLs), number of transceiver architectures have been proposed [7–18]. These methods generally aim to reduce the working frequency of the PLLs so that up-conversion or down-conversion of the signals is carried out at a lower frequency or in two steps. Furthermore, depending on the envisioned applications, one architecture might be preferred over another.

At circuit level design, the challenges are multi-fold. Low frequency circuits are not easily scalable to 60 GHz as the foundry transistor models are usually not characterized uptil this frequency. The parasitic elements of transistors also contribute to reduced high frequency performance. Consequently, considerable design margins have to be maintained resulting in power and silicon area penalty. Furthermore, few initial dry-runs are required to characterize the devices resulting in increased design times. Similarly, passives such as inductors and transformers etc., though become affordable in terms of silicon footprint, pose modeling related uncertainties and require meticulous electromagnetic (EM)-simulations. The quality factor (Q-factor) of varactors, which are invariably employed for capacitive tuning in voltage controlled oscillators (VCOs), frequency dividers etc, becomes very low. Low-ohmic substrate is also a hindrance in high-Q passive design. The technology scaling to sub-nanometer technologies reduces the supply and breakdown voltages, whereas the threshold voltage of transistors does not scale with the same order, resulting in a limited choice of reliable circuit topologies.

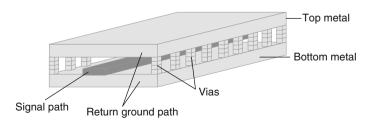

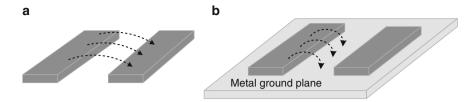

At layout level, as the wavelength of on-chip signals approach circuit dimensions, the interconnect between components becomes crucial part of design. These interconnects have to be simulated in EM solvers to incorporate the affect on circuit performance. Depending on the type of interconnect, this step is generally time consuming especially if multiple metal layers and vias are included. Furthermore, due to close proximity of components the overall layout also needs to be simulated for unwanted coupling and losses. Layout parasitics are also a major contributor for frequency shift and performance degradation and demand careful RLC extraction. Asymmetric layout of the RF paths at 60 GHz is a potential issue especially in circuits requiring phase accuracy. The typical layout approach of "smaller the better" at 60 GHz is sometimes contradictory to the symmetry requirement and some compromise has to be adopted. The measurement of 60 GHz and millimeter wave circuits, pose a different set of challenges. Dedicated measurement equipment, components and setup is required for high frequency measurements. In some cases, when direct measurement of a parameter is not possible, in-direct methods are employed which are source of measurement errors. In order to shift the measurement plane to the device-under-test (DUT), accurate calibration and de-embedding is required. The losses and mismatch associated with cables, connectors, adapters have to be carefully accounted for. The stability and repeatability of accurate measurements is also an important challenge in high frequency measurements.

The challenges at 60 GHz related to circuit, layout, measurement and technology, mentioned in the preceding discussion, assist to select the set of problems which will be tackled in this book.

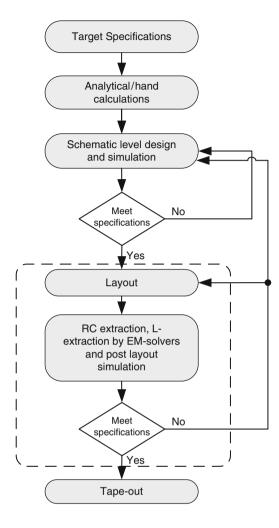

Firstly, due to the application dependence, there is no preferred transceiver architecture for 60 GHz. Thus, several different architectures can be expected in future. In order to cater for more than one application, a flexible synthesizer architecture will therefore be required. Moreover, such a multipurpose synthesizer will be expected to reuse some of its components to reduce design overhead. Secondly, a lack of design paradigm for 60 GHz is witnessed where the layout intricacies and measurement issues are understudied and lastly, the profound impact of parasitics necessitates the need of modification in the design flow of mm-wave integrated circuits. Adopting a top-down approach, this book addresses the above three problems by:

- System level analysis, design and realization of a flexible phase-locked loop suitable for a number of frequency up/down-conversion choices in a 60 GHz transceiver.

- Identifying the critical components of the synthesizer and characterizing them individually before complete system integration.

- Characterizing of passives, such as inductors, transformers and transmission lines that are extensively utilized in 60 GHz IC design.

- Revisiting the mm-wave IC design flow and incorporating the impact of parasitics (from circuit as well as layout) at an advanced stage of the design cycle.

- Identifying measurement issues for mm-wave circuits and providing possible solutions.

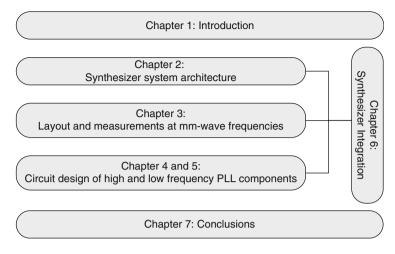

The structure of this book is illustrated in Fig. 1.5. In Chapter 2, after a brief overview of IEEE standardization for 60 GHz band and frequency conversion choices, a flexible PLL architecture is proposed. Based on theoretical analyses and system simulations of this architecture, target specifications are laid down for the PLL.

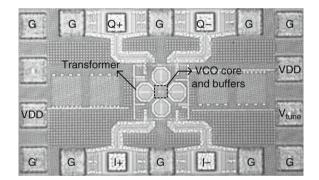

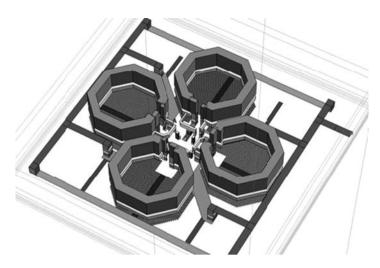

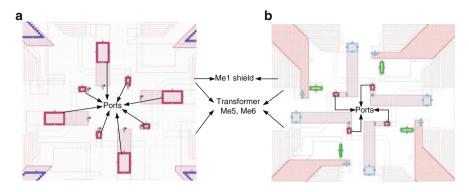

Chapter 3 discusses the layout and measurement techniques widely employed throughout this work. The circuit design of PLL components is divided in two chapters. The high frequency components, namely prescaler and voltage control oscillator (VCO) are discussed in Chapter 4. A variety of prescaler architectures are compared and two types are designed and measured. A number of VCOs are designed and measured with attention on improvement of tank quality factor,

Fig. 1.5 Structure of the book

modeling of tank inductor and transformers, and compact and symmetrical layouting techniques. The low frequency components such as the feedback divider chain, phase frequency detector (PFD), charge pump (CP) and loop filter are presented in Chapter 5. Optimization techniques for feedback divider chain, dead-zone removal in PFD and accurate current matching in CP are also discussed in this chapter.

Chapter 6 presents the integration of the complete PLL and discusses solutions for different frequency conversion choices. It is observed that connecting different blocks with perfect frequency alignment is much more challenging than designing individual blocks. This is because any unexpected parasitic of the interface between the blocks can potentially cause significant shift in the VCO and dividers, causing reduction in PLL locking range or in worst case prohibiting the loop from locking. A comparison to target specifications is also included in this chapter. The conclusions of this book are presented in Chapter 7.

### Chapter 2 Synthesizer System Architecture

**Abstract** This chapter discusses the system level aspects of frequency synthesizer design for 60 GHz. The IEEE 802.15.3c standard determines the frequency channelization of the 60 GHz band, based on which the frequency planning is carried out. A number of in-direct PLL architectures can be used for 60 GHz transceivers which are discussed in detail. Based on the proposed synthesizer architecture, the analytical calculations and system level simulations are presented. The chapter concludes by enlisting the target specifications for the proposed synthesizer.

**Keywords** IEEE 802.15.3c  $\cdot$  60 GHz  $\cdot$  Phase-locked loop  $\cdot$  Frequency synthesizer  $\cdot$  Advanced design systems  $\cdot$  Phase noise  $\cdot$  Open-loop gain  $\cdot$  Phase margin

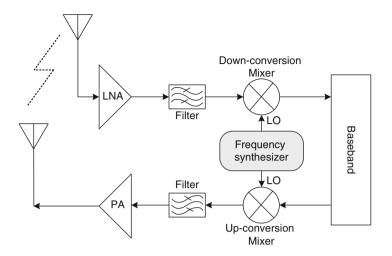

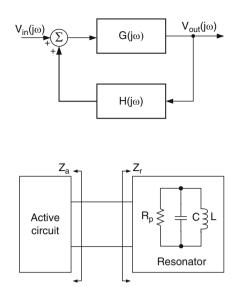

A phase-locked loop is an important block of transceivers and exists in the majority of wireless communication systems. Its application varies from generation, recovery and distribution of clock signals to jitter and noise reduction. They are also utilized to implement spread spectrum techniques to reduce interference with high-Q receivers and as a de-skewing block to phase match the clock in electronic systems. The most extensive use of PLLs is for frequency synthesis (also focus of this book), in which they are used to generate a local oscillator signal for up-conversion in a transmitter and down-conversion in a receiver as shown in Fig. 2.1. The requirements and architecture of a synthesizer depend on the system specifications which are based on the underlying regulatory standard. Performance parameters like tuning range, channel spacing or step size, spectral purity, phase noise, output power, settling time and spurious are some of the specifications required before the design phase.

The regulatory efforts for 60 GHz band are being carried at two fronts. IEEE has assigned a task group 3c for developing a millimeter-wave based alternative physical layer (PHY) for the existing 802.15.3 standard [19]. The second effort is by industrial consortiums such as WirelessHD<sup>™</sup> and ECMA International. The WirelessHD alliance has proposed a protocol that enables consumer devices to create a wireless video area network for streaming high-definition content between source and display devices [20]. ECMA International on the other hand published its 60

Fig. 2.1 A general transceiver block diagram

GHz industrial standard in December 2008. In addition to 60 GHz PHY, this standard includes MAC and HDMI PAL specifications for short range gigabit per second wireless transmission for both bulk data transfer and multimedia streaming [21]. Section 2.1 discusses the IEEE 802.15.3c channelization proposals with particular focus on PLL requirements.

Integrated circuits at 60 GHz involve significant challenges at system, circuit and layout levels as discussed in Chapter 1. However, some of these can be mitigated by taking advantage of the capabilities available at one level to relax the requirements imposed at another. For instance, to ease the requirements of a frequency synthesizer at system level, special transceiver architectures for up-conversion and down-conversion of data can be envisioned. Termed as frequency conversion (FC) techniques in this book they generally aim to operate the synthesizer at a sub-LO frequency and generate the 60 GHz LO signals indirectly. Adopting this approach makes a wide variety of architectures possible by selecting different LO frequency combinations along with the synthesizer. Consequently, each resulting architecture requires a specific synthesizer and a need for a flexible synthesizer is naturally felt. This chapter proposes a flexible PLL which can be utilized for a number of 60 GHz FC techniques. While minimizing overhead, the focus is to re-use a considerable portion of the PLL and provide flexibility at the same time. The 60 GHz FC techniques are categorized in Section 2.2, and Section 2.3 presents the proposed synthesizer architecture.

Analytical calculations and system simulations using tools such as Advanced Design System (ADS) provide a first insight into the required specifications of the PLL and its individual sub-components. Section 2.4 includes the theoretical analysis of the PLL system and, aided with simulations, leads to the target specifications mentioned in Section 2.6. The conclusions of the chapter are presented in Section 2.7.

#### 2.1 IEEE 802.15.3c Channelization

The IEEE 802.15.3 Task Group 3c (TG3c) was formed in March 2005. It is developing a millimeter-wave-based alternative physical layer (PHY) for the existing 802.15.3 wireless personal area network (WPAN) standard 802.15.3-2003. The standard is still a work in progress, and when completed, is expected to provide the first widespread international physical layer framework to support consumer 60 GHz WPANs. In September 2007, after merging and narrowing down, the task group confined its selection for 60 GHz physical layer to two proposals. These two proposals offer different possibilities of spectrum occupancy, transmission modes, modulation schemes, packet and frame structure, beam forming etc.

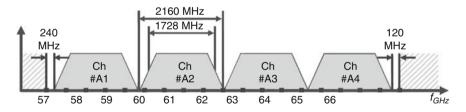

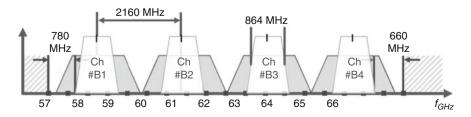

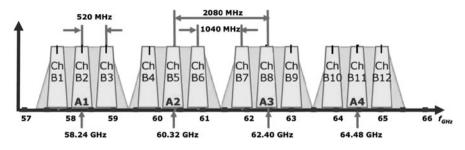

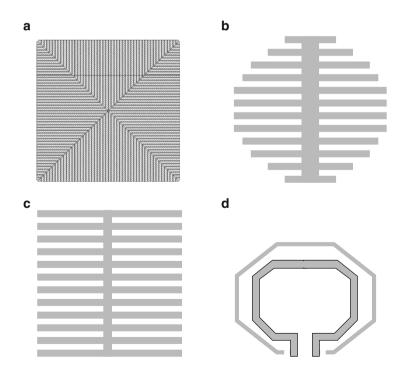

The channelization proposals for the 60 GHz band are based on high rate PHY (HRP) and low rate (LRP). The use of each depends on the data rate requirement for a certain type of communication. The HRP, having a bandwidth of 2 GHz, is used for high definition video streaming, file transfer and similar applications where multi-gigabit per second data rate is required. The channelization is shown in Fig. 2.2. The LRP, on the other hand, is used for relatively low data rate asynchronous transfer such as compressed audio, control commands including pilot, beacon and acknowledgment signals, etc. There are two proposals for the low rate channelization of four 2 GHz channels either contains four 1 GHz channels or twelve 500 MHz channels. The channelization for LRP is shown in Figs. 2.3 and 2.4, respectively.

It can be noted that the center frequencies for 1 and 2 GHz channels are identical and only differ in the guard band between two adjacent channels. The spectrum utilization of the 500 MHz sub-channels is better than the 1 GHz ones and at least

Fig. 2.2 High data rate channelization with 2 GHz bandwidth [19]

Fig. 2.3 Low data rate channelization with 1 GHz bandwidth [19]

Fig. 2.4 Low data rate channelization with 500 MHz bandwidth [19]

nine out of 12 channels are available in all regions. The above mentioned channelization is important for a 60 GHz PLL design as it determines the frequencies required from the PLL and also some in-direct specifications such as reference frequency, loop bandwidth, etc. These proposals also indicate that, if such a channelization is finalized, the PLL should be able to generate all 2 GHz as well as all sub-channels of 1 GHz and 500 MHz.

#### 2.2 60 GHz Frequency Conversion Techniques

As mentioned briefly in Chapter 1, the PLL (as frequency synthesizer) related challenges at millimeter wave frequencies is one of the dominating factors in transceiver design and necessitates the development of "synthesizer-friendly" transceivers. The generation, division and distribution of a mm-wave LO (signal used for up- and down-conversion) becomes so demanding that the choice of transmitter (TX) and receiver (RX) architectures become closely intertwined with the synthesizer design [22].

Therefore it is pertinent to categorize the approaches for up- and downconversion (or frequency conversion) of data for 60 GHz transceivers which will also determine the associated synthesizer architectures. The general aim is to reduce the operation frequency of the synthesizer while maintaining a robust overall system.

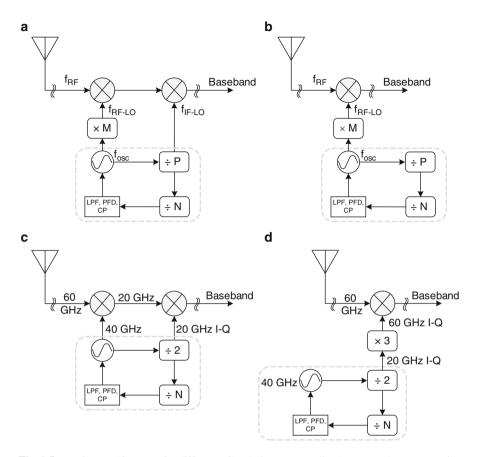

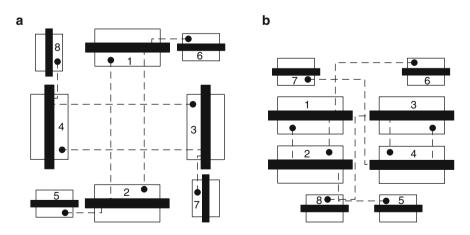

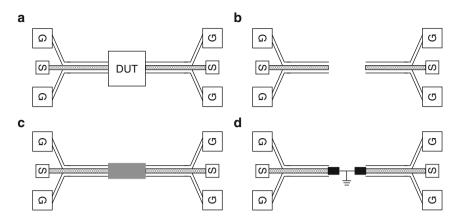

The first category in Fig. 2.5a illustrates a two step down-conversion method, a special case of which is referred to sliding-IF architecture. The incoming RF signal  $f_{RF}$  is first down-converted by mixing with the RF local oscillator signal  $f_{RF-LO}$  producing a difference (and sum) component at  $f_{RF} - f_{RF-LO}$ . The second down-conversion to baseband is achieved by using the output of the prescaler of the frequency synthesizer  $f_{IF-LO}$ . The factor 'M' refers to an integer frequency multiplier which can have a usually range between 1 and 3. The value of 1 implies a direct connection between the oscillator and the mixer whereas a value of 2 and 3 implies a frequency doubler and tripler, respectively. The factor 'P' is the

**Fig. 2.5** Receiver architectures for different FC techniques: generalized two step down-conversion (sliding-IF) (**a**), generalized single step down-conversion (**b**), an example of two step down-conversion (**c**), and an example of single step down-conversion using a frequency tripler (**d**)

division ratio of the prescaler and can also have a value between 1 and 3. The overall division ratio of the synthesizer is separated into 'P' and 'N' as the prescaler requirements and utilization in millimeter-wave synthesizers is distinct from the lower frequency divider chain. The frequency conversion to baseband is carried out as

$$f_{RF} - (f_{RF-LO} - f_{IF-LO}) = 0 (2.1)$$

where  $f_{RF-LO} = f_{OSC} \times M$  and  $f_{IF-LO} = f_{OSC} / P$ . Therefore, (2.1) can be re-written as

$$f_{RF} - f_{osc} \times M = \frac{f_{osc}}{P} \quad \text{and} \\ f_{osc} = f_{RF} \left(\frac{P}{MP+1}\right)$$

(2.2)

Using values for M and P between 1 and 3 in (2.2) yields synthesizers operating at varying frequencies. For instance M = 1, P = 1 implies the synthesizer operates at 30 GHz and provides both the RF-LO and IF-LO signals. This architecture, termed as "half-RF", is presented in [13]. This solution, although offering the lowest possible LO without doublers or triplers, has two major drawbacks: third harmonic image and LO-IF feed-through.

The values M = 1, P = 2 yield a synthesizer operating at 40 GHz shown in Fig. 2.5c. The required quadrature IF-LO is provided by the prescaler to down-convert the 20 GHz IF signal to baseband. Another demonstrated architecture uses M = 3, P = 2 by operating the synthesizer at ~17 GHz and using a frequency tripler to down-convert the RF signal to 8.5 GHz. The conversion to baseband is again using the outputs of the prescaler [23]. Another interesting frequency conversion is achieved by using M = 2, P = 2 which uses 24 GHz synthesizer and 48 and 12 GHz as the first and second down-conversion steps. Other combinations for a two step down conversion are shown in Table 2.1.

The second category of frequency conversion techniques is based on a single step down-conversion using a  $f_{RE-LO}$  of 60 GHz as shown in Fig. 2.5b. In this case, the LO frequency can be obtained either directly from a synthesizer or indirectly by using a frequency multiplier (M) in combination with a synthesizer. For instance M = 1yields a frequency synthesizer operating at 60 GHz. Termed as a direct conversion or zero-IF architecture, it uses 60 GHz quadrature LO from the synthesizer to downconvert the RF signal directly to baseband. In addition to the known issues of LO leakage, DC-offset and IP2, generation of accurate quadrature LO phases at 60 GHz, is a difficult task. In addition, division and distribution of 60 GHz LO also pose critical challenges [12, 22, 24]. For M = 3, Fig. 2.5d depicts a direct-conversion receiver with the synthesizer running at 40 GHz. The output in this case is obtained from the prescaler instead of the VCO as some prescaler architectures provide inherent quadrature signals and do not need extra circuits to generate I-O outputs as in case of VCOs. The prescaler output is translated to a 60 GHz quadrature LO using a frequency tripler as presented in [25]. Another direct conversion topology is possible by using a 30 GHz synthesizer and a frequency doubler (M = 2) to generate 60 GHz quadrature LO signals. The use of frequency doublers and triplers, although reduces the synthesizer frequency, requires innovative design techniques to overcome their lossy behavior at these frequencies. Furthermore, generation and distribution of quadrature phases from these components has to be achieved.

| Table 2.1   Synthesizer                       | М | Р | fosc(GHz) | f <sub>IF-LO</sub> (GHz) |

|-----------------------------------------------|---|---|-----------|--------------------------|

| frequencies for different values of frequency | 1 | 1 | 30        | 30                       |

| multipliers (M) and prescaler                 |   | 2 | 40        | 20                       |

| · · · ·                                       |   | 3 | 45        | 15                       |

| division ratios (P)                           | 2 | 1 | 20        | 20                       |

|                                               |   | 2 | 24        | 12                       |

|                                               |   | 3 | 25.7      | 8.5                      |

|                                               | 3 | 1 | 15        | 15                       |

|                                               |   | 2 | 17        | 8.5                      |

|                                               |   | 3 | 18        | 6                        |

#### 2.3 Proposed PLL Architecture: Flexible, Reusable, Multi-frequency

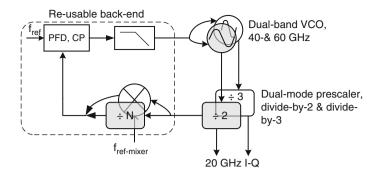

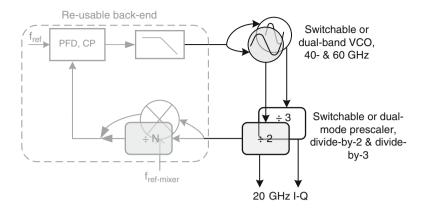

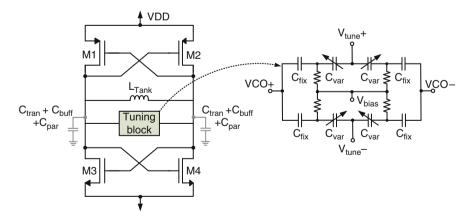

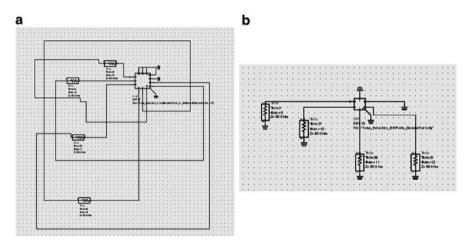

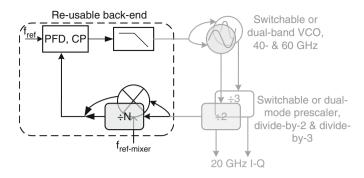

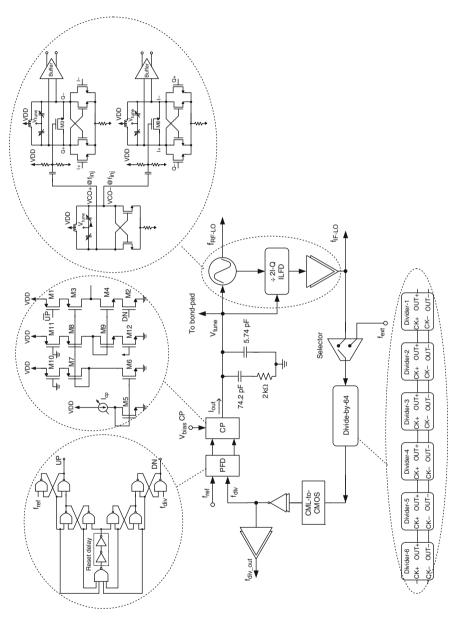

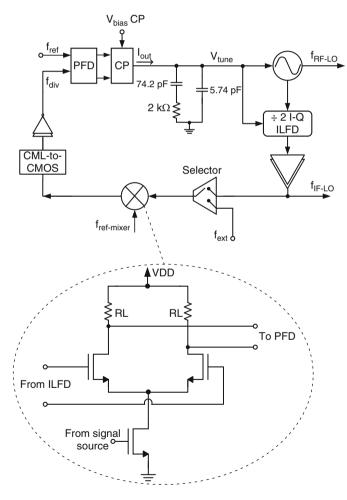

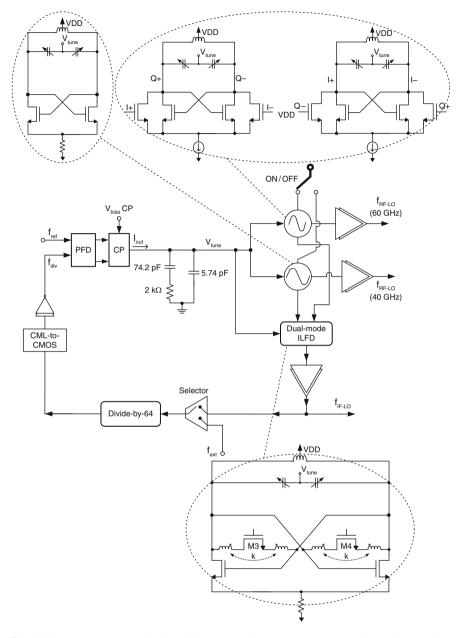

The considerable number of frequency conversion techniques elaborated in the previous section motivates the need for a flexible PLL system. The high frequency components of the synthesizer, namely VCO and prescaler are termed as the PLL front-end in this work, whereas the low frequency components including the divider-chain, phase frequency detector, charge pump and loop filter are labeled as the PLL back-end. The proposed synthesizer (shown in Fig. 2.6), while keeping the back-end fixed, aims to provide a flexible front-end enabling its application for a number of FC techniques.

The starting point of the proposed synthesizer is the architecture in Fig. 2.5c. The incoming RF signal is mixed with a nominal LO frequency of 40 GHz, generating an IF frequency of 20 GHz. The IF signal is then down-converted to baseband using the quadrature outputs from the first divider stage. This architecture, called sliding-IF, is different from its conventional dual-conversion counterpart as it requires only one synthesizer to generate the RF and IF local oscillator signals. The use of the sliding-IF topology offers the following advantages:

- The RF-LO generation takes place at 40 GHz without the need of quadrature phases.

- Using  $f_{osc} = 2/3 \times F_{rf}$  reduces the required 60 GHz bandwidth (B) by the same factor, i.e.  $2/3 \times B$  is needed at 40 GHz. This is especially beneficial as achieving 7 GHz of tuning range for VCOs at 60 GHz is a considerable challenge.

- The frequency division in the prescaler also occurs at 40 GHz increasing the possibility of utilizing different frequency divider topologies.

- Distribution and layout issues for 40 GHz differential LO are less severe than quadrature 60 GHz signals.

The second usage of the proposed PLL is shown in the direct-conversion topology of Fig. 2.5d where a frequency tripler, using the 20 GHz quadrature phases from the prescaler output, generates the 60 GHz quadrature LO signals. The requirement from an academic partner (in the WiComm project) for a 20 GHz quadrature LO further augments this choice and will be explained in the next section.

Another flexibility in the synthesizer topology is motivated by the possible re-usability of the PLL back-end. As shown in Fig. 2.6, by designing a dual-band or switchable VCO operating at 40- and 60 GHz, and a dual-mode (or switchable) prescaler capable of divide-by-2 and divide-by-3 operation, the proposed synthesizer can also operate in a direct-conversion topology without the frequency tripler. The re-usability of a power hungry and area consuming PLL back-end is a substantial advantage. However, meeting the performance specifications simultaneously, at 40- and 60 GHz, in these dual-mode components is a challenging part of design.

The divider chain, next to the prescaler usually consists of cascaded frequency dividers. In this work, we propose an alternative of the divider chain and replace it

Fig. 2.6 Proposed PLL architecture suitable for sliding-IF and direct-conversion with and without tripler

with a mixer to directly down-convert the prescaler output frequency close to reference frequency for phase and frequency comparison. The different channelization proposals of the IEEE 802.15.3c standard explained in Section 2.1 signify the need for careful frequency planning of the synthesizer. The proposed synthesizer aims to support the 2 GHz HRP channels as well as 1 GHz and 500 MHz LRP channels, making it a multi-frequency PLL.

Summarizing, the proposed synthesizer envisions firstly, the sliding-IF topology, secondly, the direct-conversion topology with or without using a frequency tripler and, while using the same PLL back-end, to support all channelization proposals of the standard.

#### 2.3.1 Utilization in WiComm Project

As mentioned in Chapter 1, the WiComm project aims to demonstrate an integrated 60 GHz transceiver. The transmitter part, being designed by an academic partner, is based on a frequency tripler, mixer and a power amplifier. The frequency tripler reported in [25] requires quadrature phases at 20 GHz to generate 60 GHz quadrature local oscillator signals. The key requirement from the synthesizer (of this work) is to provide 20 GHz quadrature signals with 0-dBm output power and a frequency range of 19–21 GHz, corresponding to an LO frequency of 57–63 GHz. On a system level, the proposed PLL topology is able to provide the required LO. The output power and frequency range specifications will be used during the circuit design of the synthesizer.

#### 2.4 System Analysis and Design

Prior to actual circuit design, investigation of the complete PLL system analytically as well as by system simulations is required to gain insight into the overall requirements. This section, after discussing PLL basics and frequency planning, presents the calculated system parameters such as phase margin, loop bandwidth and component specific parameters such as VCO gain, charge pump current and loop-filter values.

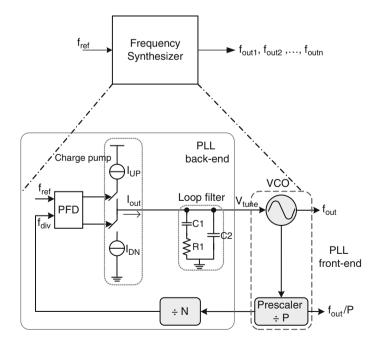

#### 2.4.1 Phase-Lock Loop Basics

Phase-locked loops, as mentioned earlier, have a variety of applications. However, in this book we will focus on their use as a frequency synthesizer. In simple terms, using a clean reference signal ( $f_{ref}$ ), a frequency synthesizer generates the channelized frequencies in order to up-convert the outgoing data for transmission and down-convert the received signal for processing.

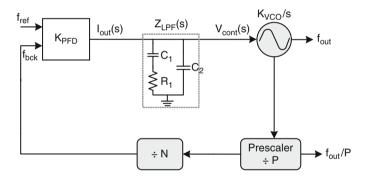

A basic frequency synthesizer consists of a phase-frequency detector (PFD), charge-pump (CP), loop filter, VCO, high-speed prescaler as a first divide stage and a series of subsequent frequency dividers (see Fig. 2.7). Due to the feedback operation, the output frequency of the above synthesizer is given by

$$f_{out} = N \times P \times f_{ref} \tag{2.3}$$

Generally, the prescaler division factor (P) is included in the overall division factor. However, in mm-wave synthesizers the requirements for prescalers are much different than the lower frequency divider chain. Therefore, they will be

Fig. 2.7 Basic frequency synthesizer block diagram

treated separately in this work. Based on the type of frequency division, the synthesizer can be broadly categorized into the following:

- Integer-N frequency synthesizer, in which the division factor  $(N \times P)$  is an integer. The frequency resolution or channelization, in this case, can only be equal to the reference frequency  $(f_{ref})$ . This can be a limitation for narrow-band applications where lower resolution is desired.

- Fractional-N frequency synthesizer, in which the division factor is a fractional number. Using such a synthesizer enables the use of a large reference frequency to achieve a small frequency resolution. The fractional division is achieved by employing dual-modulus or multi-modulus frequency dividers. The down-side of fractional-N synthesizers is the appearance of fractional spurs within the loop bandwidth which, for practical applications, have to be suppressed to an acceptable level. Techniques such as Sigma-Delta modulation have been used to control the loop divider such that fractional spurs can be randomized and shifted to a higher frequency band where they can be easily removed by the loop filter.

As this book targets the 60 GHz wireless transmission system which is a wideband system, the main focus will be on integer-N frequency synthesizers.

The basic operation of a synthesizer starts with a clean reference signal ( $f_{ref}$ ) which in most cases is a crystal oscillator. This acts as one input of the phase-frequency detector whereas the second input is the feedback signal from the divider chain ( $f_{div}$ ). The PFD compares the incoming signals and generates voltage pulses proportional to the phase difference between them. These UP and DN pulses control the switches in the charge-pump, which converts them into current ( $I_{DN}$  or  $I_{UP}$ ) pulses. The current is then converted to a stable DC voltage by a low pass filter. This DC voltage ( $V_{tune}$ ) acts as a tuning voltage and adjusts the output of the VCO, such that its phase, when divided by the division factor, is equal to the phase of the reference frequency. In the locked state, the phase difference reaches zero (or a finite value) and the output is a clean single-tone frequency.

The type and order of a synthesizer, which are widely used for PLL nomenclature, is determined by the number of poles at the origin and the total number of poles in the system, respectively. Due to their integrative nature, VCOs have a pole at the origin making all PLLs at least a type-I, first order system. In order to track a frequency step, as required in a frequency synthesizer, another pole at DC is required so that the phase error could be reduced to zero. This pole is accomplished by adding a capacitor (C1 in Fig. 2.7) making the overall PLL a type-II, second order synthesizer. The presence of two poles at the origin causes stability issues, which can be countered by adding a series resistor (R1 in Fig. 2.7) with the capacitor. This introduces a zero in the transfer function hence stabilizing the loop. However, the current pulses generated by the charge pump in every comparison cycle cause a voltage ripple on the VCO control voltage. This ripple deteriorates the spectral purity by modulating the VCO and generating frequency spurs. To overcome this, a second capacitor (C2 in Fig. 2.7) is added to smoothen the control voltage. The addition of this pole categorizes the PLL as a type-II, third order system. By introducing more poles to further suppress the frequency spurs and noise, higher type and order PLLs are also possible. However, they are rarely used as loop stability becomes a serious concern.

#### 2.4.2 Frequency Planning

The frequency planning of the synthesizer is one of the initial steps in system design. Based on the channelization proposals described in Section 2.1, the frequency resolution, which is the minimum frequency step the synthesizer can generate, is determined. The frequency resolution is then used to determine other PLL system parameters in the next section.

The frequency planning is treated in two steps. First, the required LO frequencies for the 40 GHz front-end are listed and next the 60 GHz PLL front-end is analyzed. It is desired that the same reference frequency is utilized for both front-ends as well as to support all HRP and LRP channelization proposals. This eases back-end design of the synthesizer considerably. As evident from Fig. 2.6, the division factor of the prescaler (P) is 2 and 3 for the front-ends, respectively, which changes the overall division ratio while keeping the reference frequency constant. The division ratios are chosen in such a way that N  $\times$  P for HRP (2 GHz and 1 GHz) channels is a subset of the division ratio of LRP (500 MHz). Along with 60 GHz, the corresponding frequencies at 40 and 20 GHz are also shown in Table 2.2 to determine the required tuning and locking range of the VCO and prescaler, respectively.

The above table provides a few insights into the requirements of the synthesizer. The LO frequency at 60 GHz spans from 57 to 64 GHz whereas the 40 GHz front-end, which is operating at 2/3 of 60 GHz, requires a locking range from 38 to 42 GHz. The frequency conversion topology involving a tripler requires frequencies from 19 to 21 GHz from the output of the prescaler. For the reference frequency of 300 MHz, the overall division ratio of 127–141 is required to satisfy both LRP and HRP channels. The center frequencies for 1 and 2 GHz channels are identical and only differ in the guard band between two adjacent channels.

The frequency planning of the synthesizer using a 60 GHz front-end is tabulated in Table 2.3. The overall division ratios are higher due to higher VCO frequency and range from 190 to 212. As the center frequencies for the 2 and 1 GHz channel are identical, they are merged in one table. The use of the same reference frequency (300 MHz) results in slightly different center frequencies and bandwidth for the 500 MHz LRP channel as compared to the 40 GHz front-end plan. However, for the proof-of-concept this difference can be ignored. The next section, using these basic requirements further analyzes the synthesizer to determine its complete set of parameters.

|                              | At 60 GHz  |             |                |                                    |

|------------------------------|------------|-------------|----------------|------------------------------------|

| 1                            | 11 00 0112 | At 40 GHz   | At 20 GHz      | $N \times P$                       |

| number                       |            |             |                | (for $f_{ref} = 300 \text{ MHz}$ ) |

| C1 5                         | 7.15       | 38.10       | 19.05          | 127                                |

| C2 5                         | 7.60       | 38.40       | 19.20          | 128                                |

| C3 5                         | 8.05       | 38.70       | 19.35          | 129                                |

| C4 5                         | 8.95       | 39.30       | 19.65          | 131                                |

| C5 5                         | 9.40       | 39.60       | 19.80          | 132                                |

| C6 5                         | 9.85       | 39.90       | 19.95          | 133                                |

| C7 6                         | 0.75       | 40.50       | 20.25          | 135                                |

| C8 6                         | 1.20       | 40.80       | 20.40          | 136                                |

| C9 6                         | 1.65       | 41.10       | 20.55          | 137                                |

| C10 6                        | 2.55       | 41.70       | 20.85          | 139                                |

| C11 6                        | 3.00       | 42.00       | 21.00          | 140                                |

| C12 6                        | 3.45       | 42.30       | 21.15          | 141                                |

| (b) For LRP channels (1 GHz) |            |             |                |                                    |

|                              | At 60 GHz  | At 40 GHz   | At 20 GHz      | $N \times P$                       |

| number                       |            |             |                | $(for f_{ref} = 300 \text{ MHz})$  |

|                              |            |             |                |                                    |

| B1 5                         | 7.60       | 38.40       | 19.20          | 128                                |

| B2 5                         | 9.40       | 39.60       | 19.80          | 132                                |

| B3 6                         | 1.20       | 40.80       | 20.40          | 136                                |

| B4 6                         | 3.00       | 42.00       | 21.00          | 140                                |

| (c)                          |            | For HRP cha | annels (2 GHz) |                                    |

| Channel A                    | At 60 GHz  | At 40 GHz   | At 20 GHz      | $N \times P$                       |

| number                       |            |             |                | (for $f_{ref} = 300 \text{ MHz}$ ) |

| A1 5                         | 7.60       | 38.40       | 19.20          | 128                                |

| A2 5                         | 9.40       | 39.60       | 19.80          | 132                                |

| A3 6                         | 1.20       | 40.80       | 20.40          | 136                                |

| A4 6                         | 3.00       | 42.00       | 21.00          | 140                                |

**Table 2.2** Frequency plan for 40 GHz PLL front-end; for LRP 500 MHz channels (a), for LRP 1 GHz channels (b), and for HRP 2 GHz channels (c)

#### 2.4.3 Synthesizer Parameters

Phase-lock loops are feedback systems which are inherently non-linear. However, their essential operation can be approximated very well by linear analysis. In such an analysis, the Laplace transform is a valuable tool. The related concept of transfer functions, which describe the s-domain relation between input and output of a linear circuit, is used to analyze the open-loop and closed-loop characteristics of the PLL.

A simplified s-domain representation of the synthesizer is shown in Fig. 2.8. The phase-frequency detector and charge-pump are merged into one block represented by a transfer parameter,  $K_{PFD}$  (equal to  $I_{cp}/2\pi$ ). The impedance of the second-order loop filter is shown as  $Z_{LPF}$ . The VCO conversion gain,  $K_{VCO}$ , represents the sensitivity of VCO frequency with tuning voltage in rad/(s × V). The division

|                | For LRP channels (500 MHz)      |                                                  |  |  |

|----------------|---------------------------------|--------------------------------------------------|--|--|

| Channel number | At 60 GHz                       | $N \times P$                                     |  |  |

|                |                                 | (for $f_{ref} = 300 \text{ MHz}$ )               |  |  |

| C1             | 57.00                           | 190                                              |  |  |

| C2             | 57.60                           | 192                                              |  |  |

| C3             | 58.20                           | 194                                              |  |  |

| C4             | 58.80                           | 196                                              |  |  |

| C5             | 59.40                           | 198                                              |  |  |

| C6             | 60.00                           | 200                                              |  |  |

| C7             | 60.60                           | 202                                              |  |  |

| C8             | 61.20                           | 204                                              |  |  |

| C9             | 61.80                           | 206                                              |  |  |

| C10            | 62.40                           | 208                                              |  |  |

| C11            | 63.00                           | 210                                              |  |  |

| C12            | 63.60                           | 212                                              |  |  |

|                | For HRP (2 GHz) and LRP (1 GHz) |                                                  |  |  |

| Channel number | At 60 GHz                       | $N \times P$                                     |  |  |

|                |                                 | $(\text{for } f_{\text{ref}} = 300 \text{ MHz})$ |  |  |

| A1, B1         | 57.60                           | 192                                              |  |  |

| A2, B2         | 59.40                           | 198                                              |  |  |

| A3, B3         | 61.20                           | 204                                              |  |  |

| A4, B4         | 63.00                           | 210                                              |  |  |

Table 2.3 Frequency plan for 60 GHz PLL front-end

Fig. 2.8 Simplified s-domain representation of the synthesizer

ratio of the prescaler and lower frequency divider chain is represented by P and N, respectively.

The open-loop transfer function of the above synthesizer can be defined as

$$H_{OL}(s) = \frac{K_{PFD} K_{VCO} Z_{LPF}(s)}{N \cdot P \cdot s}$$

(2.4)

which shows a pole at the origin due to the VCO. The over-all loop dynamics are determined by the transfer-function of the loop-filter, which in this case is an

impedance function, as it converts the charge-pump current to a tuning voltage for the VCO.  $Z_{LPF}(s)$  is expressed as

$$Z_{LPF}(s) = \frac{1 + sR_1C_1}{s(sR_1C_1C_2 + C_1 + C_2)}$$

(2.5)

Equation (2.5) shows the first loop-filter pole at  $\omega_{p1} = 0$  and the zero at

$$\omega_z = 1/R_1 C_1 \tag{2.6}$$

The two poles at the origin (first one due to VCO and second one,  $\omega_{p1}$ ) can render the loop unstable as the phase-margin is zero. The addition of  $\omega_z$  stabilizes the loop and proper positioning can provide sufficient phase-margin to ensure loop stability as will be discussed shortly. To obtain a meaningful expression for the second pole, which relates it with  $\omega_z$ , (2.5) is re-arranged by introducing a variable  $m = (C_1 + C_2)/C_2$  as

$$Z_{LPF}(s) = R_1 \frac{1 + s/\omega_z}{s\left(1 + \frac{s}{\frac{C_1 + C_2}{R_1 C_1 C_2}}\right)/\omega_z} \frac{m - 1}{m}$$

(2.7)

which shows the second loop-filter pole at

$$\omega_{p2} = \frac{1}{R_1 C_1} \frac{C_1 + C_2}{C_2} = m\omega_z \tag{2.8}$$

and thus simplifying Z<sub>LPF</sub>(s) as

$$Z_{LPF}(s) = R_1 \frac{1 + s/\omega_z}{s\left(1 + \frac{s}{\omega_{p2}}\right)/\omega_z} \frac{m-1}{m}$$

(2.9)

Using (2.9), the open-loop transfer function of (2.4) can be re-written as

$$H_{OL}(s) = A \frac{1 + s/\omega_z}{s^2 \left(1 + \frac{s}{\omega_{p2}}\right)/\omega_z} \frac{m-1}{m}$$

(2.10)

where A is

$$A = \frac{K_{PFD} K_{VCO} R_1}{N \cdot P} \tag{2.11}$$

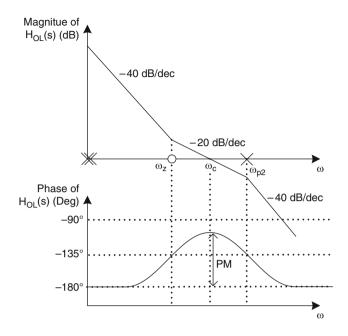

The magnitude and phase of the open-loop transfer function can be drawn in a Bode plot to get insight into poles and zero positions and conditions for stability of

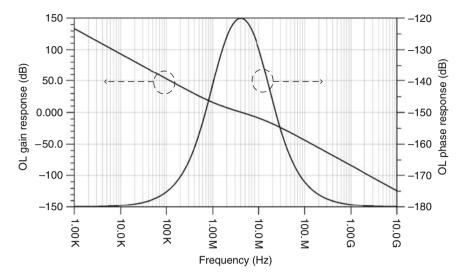

Fig. 2.9 Open-loop magnitude and phase response

the loop. This is illustrated in Fig. 2.9. The zero at  $\omega_z$  decreases the slope from 40 to 20 dB/dec and more importantly increases the phase from  $-180^{\circ}$ . The value of the phase, where magnitude is unity or 0-dB, is called the phase margin (PM). The frequency of the cross-over point is the loop bandwidth of the PLL denoted by  $\omega_c$ . The latter is calculated by equating the magnitude of (2.10) to unity which yields

$$\omega_c = A \, \frac{m-1}{m} \frac{\cos(\Phi_{p2})}{\sin(\Phi_z)} \tag{2.12}$$

where  $\Phi_z = \tan^{-1}(\omega_c/\omega_z)$  and  $\Phi_{p2} = \tan^{-1}(\omega_c/\omega_{p2})$ . The phase-margin can be expressed as

$$\Phi_m = -180^\circ + \Phi_z - \Phi_{p2} = 180^\circ + \tan^{-1}\left(\frac{\omega_c}{\omega_z}\right) - \tan^{-1}\left(\frac{\omega_c}{\omega_{p2}}\right)$$

(2.13)

Ideally, the phase-margin should be maximized to ensure loop stability and also to cater for variations in resistance and capacitance values which determine the poles and zero positions. The maximum possible phase-margin can be found by differentiating (2.13) and solving for  $\omega_c$  as

$$(\omega_c)_{for \max PM} = \sqrt{\omega_z \, \omega_{p2}} = \sqrt{m} \, \omega_z \tag{2.14}$$

Substituting  $\omega_c$  in (2.13) yields the maximum phase-margin as

$$(\Phi_m)_{\max} = -180^\circ + \tan^{-1}\sqrt{\frac{\omega_{p2}}{\omega_z}} - \tan^{-1}\sqrt{\frac{\omega_z}{\omega_{p2}}} = \tan^{-1}\frac{(m-1)}{2\sqrt{m}}$$

(2.15)

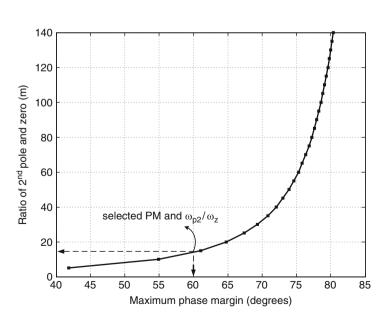

Equations (2.14) and (2.15) show that, firstly, for optimal stability (maximum PM), the unity gain crossover point should be the geometric mean of the zero and second pole as this is the position where the phase is farthest from 180°. Secondly, the maximum phase-margin is exclusively determined by the capacitor ratio (m) which is also the ratio of the second pole ( $\omega_{p2}$ ) and zero ( $\omega_z$ ). Figure 2.10 shows the phase margin for different values of m. It is noticed that due to the arc-tangent function the curve is asymptotic to 90°.

Using  $\Phi_z = \tan^{-1}(\sqrt{m})$  and  $\Phi_{p2} = \tan^{-1}(1/\sqrt{m})$ , it is observed that  $\sin(\Phi_z) = \cos(\Phi_{p2})$  which simplifies (2.12) to

$$\omega_c = A \, \frac{m-1}{m} = \frac{K_{PFD} \, K_{VCO} \, R_1}{N \cdot P} \, \frac{m-1}{m} = \frac{K_{PFD} \, K_{VCO} \, R_1}{N \cdot P} \frac{C_1}{C_1 + C_2} \tag{2.16}$$

The closed-loop transfer function of the type-II, third-order PLL is given by

$H_{CL}(s) = \frac{1 + s/\omega_z}{1 + \frac{s}{\omega_z} + \frac{s^2}{K\omega_z \frac{m-1}{m}} \left(1 + \frac{s}{\omega_{p2}}\right)}$ (2.17)

Fig. 2.10 Maximum phase margin vs. ratio of second pole  $(\omega_{p2})$  and zero  $(\omega_z)$

The frequency planning covered in the previous section and the above mentioned expressions will be employed to determine the PLL parameters next:

- The specified output frequencies in Tables 2.2 and 2.3 define the required tuning range of the VCOs and this, together with the supply voltage determines the associated gain,  $K_{VCO}$ . For the 40 GHz front-end the VCO requires a tuning range from 38 to 42.3 GHz. Supposing a VCO tuning voltage of 1.2 V (nominal supply for sub-nanometer CMOS technologies), the resulting VCO gain is equal to  $K_{VCO} = 2\pi \times 3.58$  G rad/s  $\times$  V. On the other hand, for the 60 GHz front-end, the required VCO tuning range is 57–63.6 GHz and the  $K_{VCO} = 2\pi \times 5.5$  G rad/s  $\times$  V. These parameters also require some safety margins to cater for PVT variations and are included during circuit design.

- The reference frequency for both front-ends is identical and equal to  $f_{ref} = 300$  MHz. The resulting division ratio range is N × P = 127–141 for the 40 GHz front-end and N × P = 190–212 for the 60 GHz front-end.

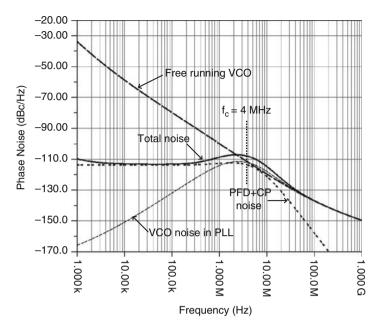

- The choice of the loop-bandwidth ( $\omega_c$ ) is an important step for the overall PLL design and a number of considerations have to be analyzed. Firstly, settling time which is defined as the time required by the loop to switch from one channel to another, is dictated by the chosen loop bandwidth. Secondly, to ensure loop stability  $\omega_c$  (or  $f_c$ ) should be a fraction of the reference frequency. This is treated in sufficient detail in [26] which estimates a condition of  $f_{ref}/10 > f_c$  for loop stability. Lastly,  $\omega_c$  affects the noise transfer characteristic of the PLL and defines the "knee" in the overall phase noise curve. This will be discussed in Section 2.6.

Having selected a  $f_{ref} = 300$  MHz, the above mentioned stability bound is satisfied (with some margin) by selecting a loop bandwidth of  $f_c = 4$  MHz. This value also results in reasonably valued loop filter components which can be integrated on-chip. There is no specification for settling time proposed in the current standard however the chosen  $f_c$  results in a settling time of  $\sim 1 \mu s$ .

• The next step is to determine the frequency of the zero  $(\omega_z)$  and second pole  $(\omega_{p2})$ . To achieve a phase margin of 60° the capacitance ratio m must equal 13.93 (see Fig. 2.10). The optimal position of the zero and pole can be calculated using (2.8) and (2.14) which show that  $\omega_c$  should be the geometric mean of  $\omega_z$  and  $\omega_{p2}$ , i.e.

$$f_z = \frac{f_c}{\sqrt{m}} = 1.072 \text{MHz} \text{ and } f_{p2} = \sqrt{m} f_c = 14.93 \text{MHz}$$

(2.18)

• Using (2.16) and a PFD gain of  $500 \ \mu A/2\pi$ , resistor and capacitor values of the loop filter can be determined. The difference in VCO gain and division ratios for the two front-ends could lead to different loop filter values. However, the ratio of

| <b>Table 2.4</b> Summary ofcalculated PLL parameters | 40 GHz front-end         | VCO tuning range<br>K <sub>VCO</sub><br>Division ratio | 38–42.3 GHz<br>3.58 GHz/V<br>127–141 |

|------------------------------------------------------|--------------------------|--------------------------------------------------------|--------------------------------------|

|                                                      | 60 GHz front-end         | VCO tuning range<br>K <sub>VCO</sub>                   | 57–63.6 GHz<br>5.5 GHz/V             |

|                                                      |                          | Divide ratio                                           | 190-212                              |

|                                                      | Reference frequency      |                                                        | 300 MHz                              |

|                                                      | Loop bandwidth           |                                                        | 4 MHz                                |

|                                                      | Charge-pump current      |                                                        | 500 μΑ                               |

|                                                      | Settling time            |                                                        | $\sim 1 \ \mu s$                     |

|                                                      | Second-order loop filter | R1                                                     | 2 kΩ                                 |

|                                                      | -                        | C1                                                     | 74.2 pF                              |

|                                                      |                          | C2                                                     | 5.74 pF                              |

selected  $K_{vco}$  and average division ratio in (2.16) closely match. Therefore, the overall calculations are unaffected and the loop filter does not require different resistance and capacitance for the two front-ends. This re-usability of the area consuming LPF saves considerable silicon area.

The calculated resistance  $R1 = 2 \text{ k}\Omega$  and (2.6) yields for the first capacitor C1 = 74.2 pF. The last loop filter component C2 = 5.74 pF is calculated using the capacitance ratio term, m.

The key PLL parameters calculated above are summarized in Table 2.4.

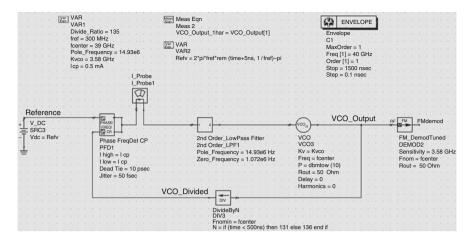

#### 2.5 System Simulations

PLL based frequency synthesizers consist of components operating at vastly different frequencies. The VCO and prescaler, operating at the highest frequencies, require a high numerical sampling rate in the simulations whereas the low frequency components like PFD have large time constants. Consequently, the simulation of such systems is not trivial as few micro-seconds transient simulation coupled with a small time step means millions of time points are required. Therefore, prior to full-blown circuit level simulations, system level simulations based on behavior models are often adopted. These simulations provide a first insight into the overall system operation and the interaction of different components with each other.

Agilent's Advanced Design System (ADS) provides an adequate tool-box for PLL related simulations. The loop's AC response to extract stability information like phase margin, dynamic behavior to obtain settling time, and noise performance are all possible using this tool. A basic simulation environment is depicted in Fig. 2.11. The LPF block is custom-made based on the second order loop filter equations. The divider is used to step the division ratio and VCO output is demodulated using the  $FM\_Demod$  block to obtain the settling time results. A similar setup, with a difference of the loop being opened, is simulated to

Fig. 2.11 ADS basic simulation environment

acquire open-loop gain and phase response of the PLL. The PFD and charge pump are merged into one block and characterized by relevant parameters like  $I_{cp}$ , deadzone time and timing jitter. The dead-zone phenomenon is an undesired characteristic of PFDs which refers to its inability to track the phase difference between the two input signals. In such a case, the output charge pump current is zero and the spurious tones appear at the VCO output un-attenuated. The timing jitter parameter models the noise in the charge pump current which corresponds to jitter at the PFD input. These two variables are assigned simulated values based on separate PFD and charge pump simulations in ADS. The current probe shows the charge pump current being pumped into the loop filter to move the synthesizer towards lock.

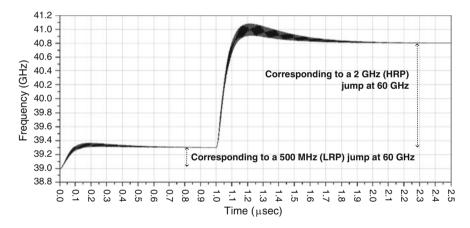

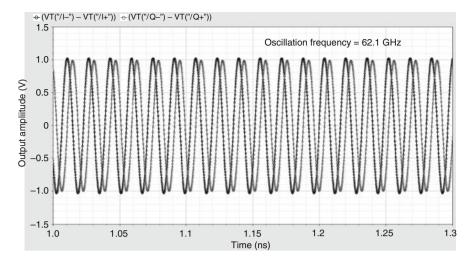

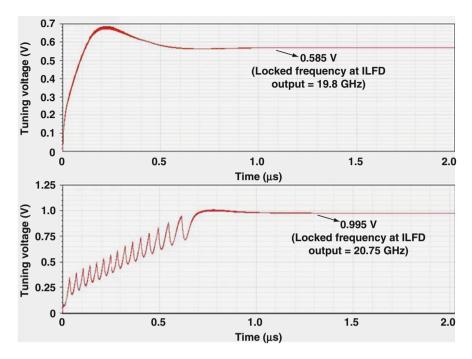

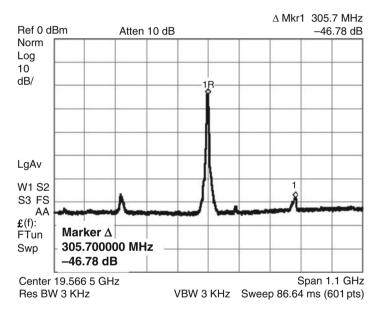

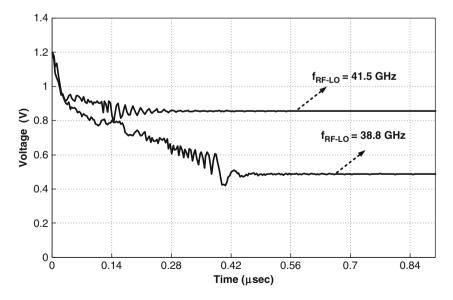

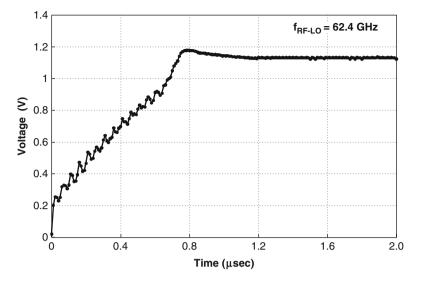

The open loop gain and phase response of the synthesizer is shown in Fig. 2.12. The gain curve reflects the system pole positions. The starting slope is -40 dB/dec due to two poles at the origin and reduces to -20 dB/dec due to the introduction of stabilizing zero ( $\omega_z$ ) at 1.072 MHz. The high frequency pole ( $\omega_{p2}$ ) at 14.93 MHz modifies the slope again to -40 dB/dec. The phase at 0-dB cross-over point is  $-120^\circ$  showing that phase margin is  $60^\circ$  as desired. To estimate the settling time, the division ratio is first changed to 131 and then incremented to 136. This corresponds to a 500 MHz and 2 GHz frequency jump at 60 GHz, respectively. The settling time obtained is about 1 µs as shown in Fig. 2.13.

The ideal output of a frequency synthesizer is a pure sinusoidal waveform. However, just like any other integrated electronic system, non-idealities such as noise degrade the spectrum purity of the output signal. This can potentially result (among other negative impacts) in lower sensitivity, poor blocking performance on the receiver side, and increased spectral emissions on the transmitter side. The output of a typical synthesizer can be expressed as

$$v_{out}(t) = V_0 \cos(f_{LO}t + \Phi_p(t))$$

(2.19)

Fig. 2.12 Open-loop gain and phase response of PLL

Fig. 2.13 Settling time corresponding to a 500 MHz and 2 GHz frequency jump

where  $f_{LO}t$  is the desired phase of the output and  $\Phi_p(t)$  models the phase fluctuation in the PLL output. Noise generated by phase fluctuations of particular interest for synthesizer performance. These fluctuations can be categorized into periodic and random variations as

$$\Phi_p(t) = \Delta \Phi_p \, \sin(2\pi f_s t) + \varphi(t) \tag{2.20}$$

The first term represents the periodic phase variations which produce discrete spurious tones at an offset frequency  $f_s$  from the carrier frequency  $f_{LO}$ . The level of

these spurs should be as low as possible as compared to the carrier to avoid up- or down-conversion to the desired frequency band after LO mixing. The second term represents the random phase variation and produces phase noise, which is a measure of how much the output diverges from a pure tone in the frequency domain.

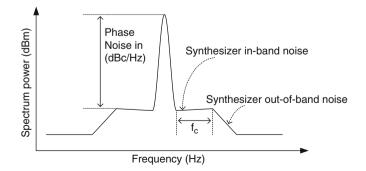

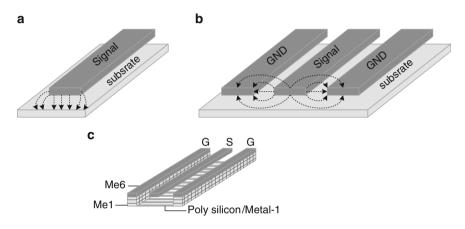

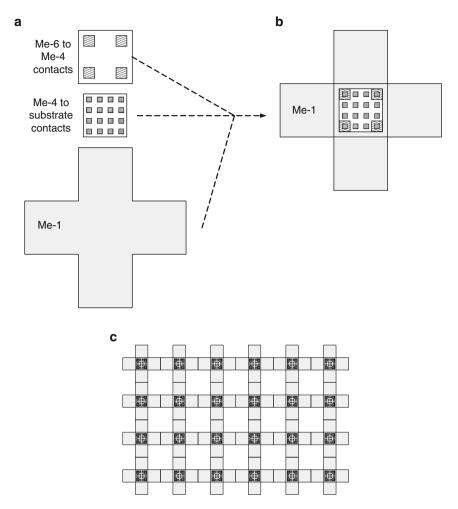

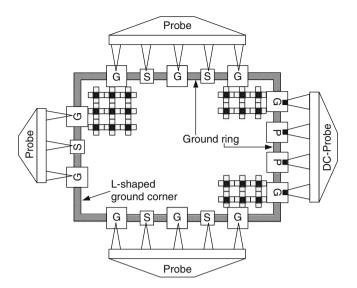

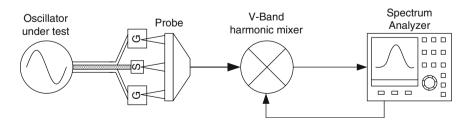

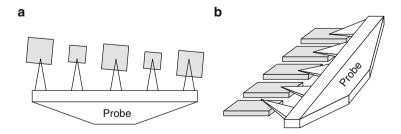

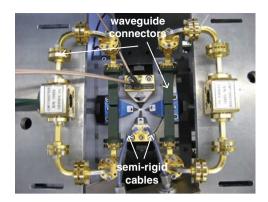

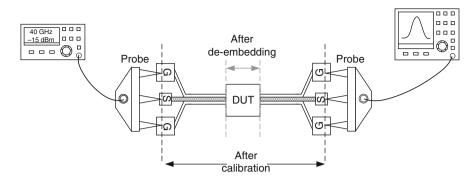

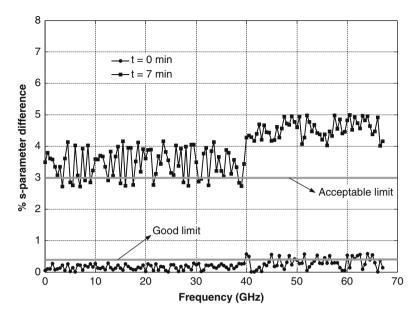

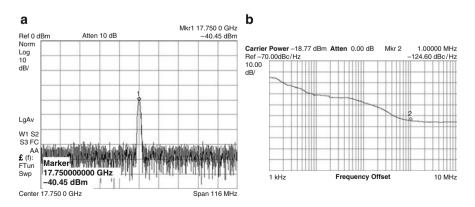

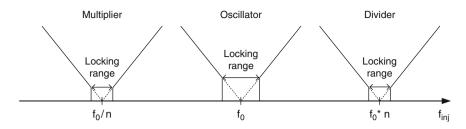

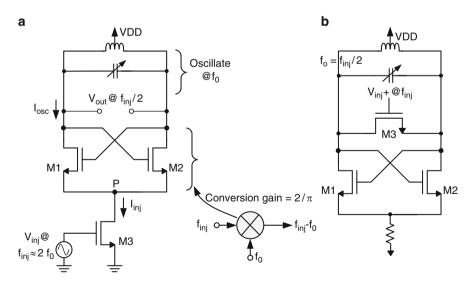

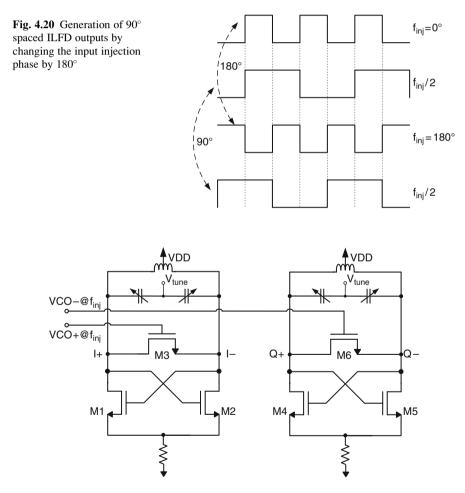

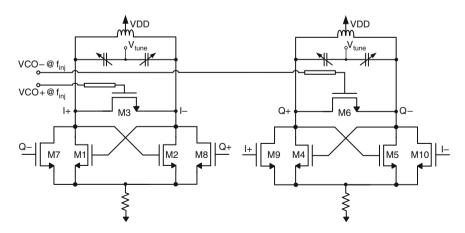

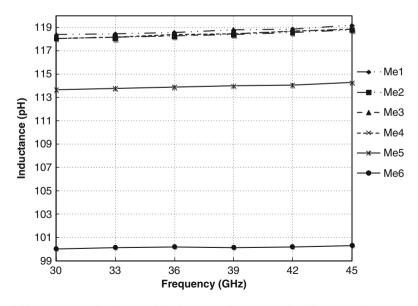

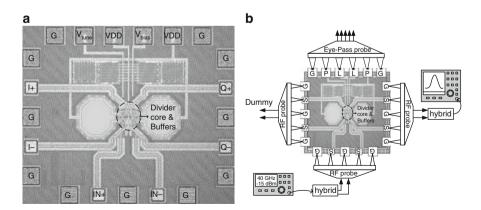

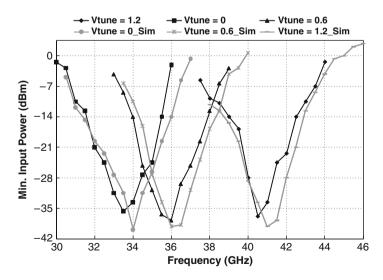

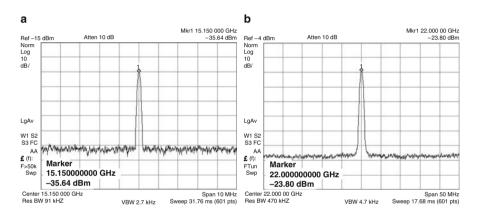

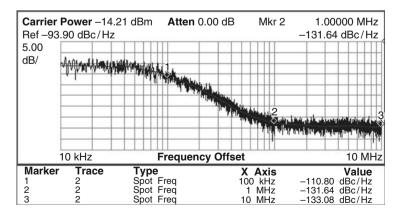

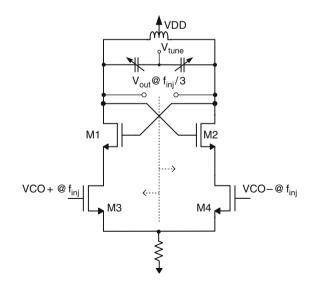

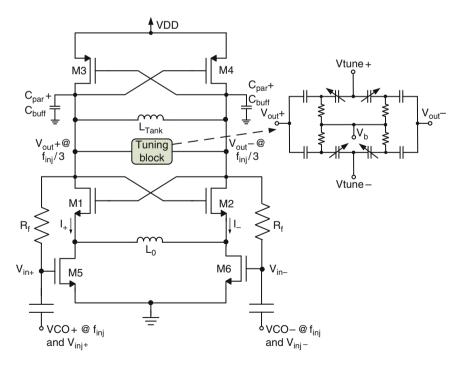

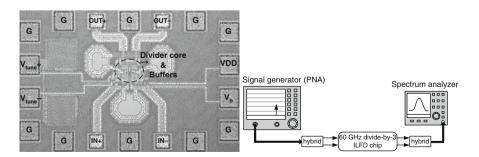

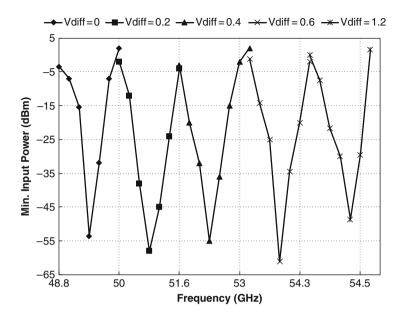

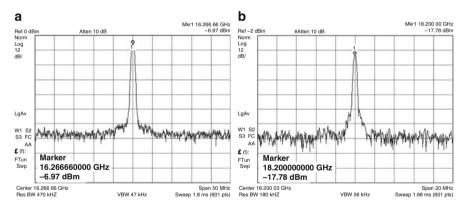

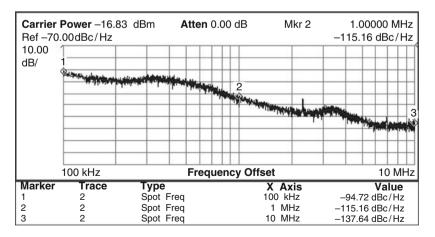

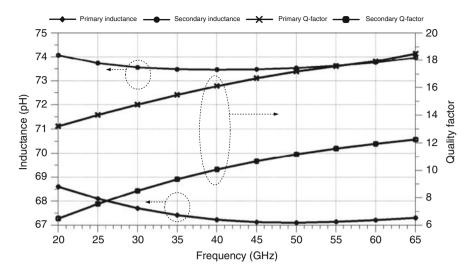

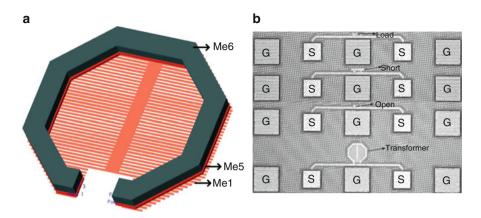

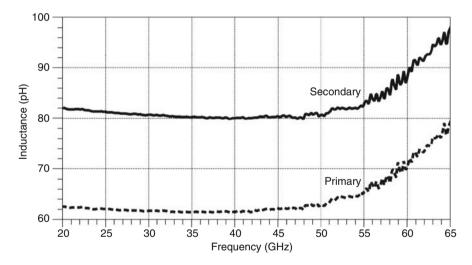

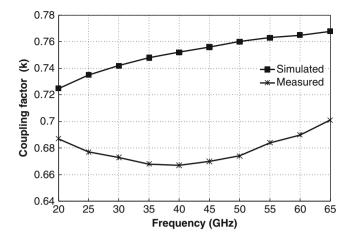

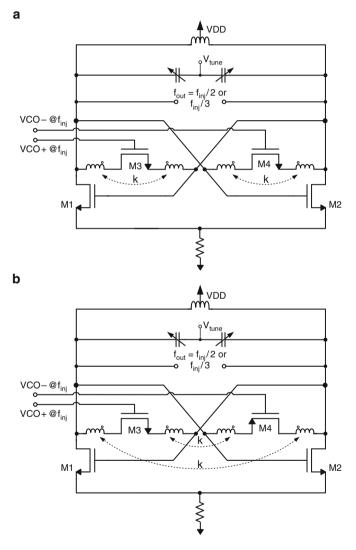

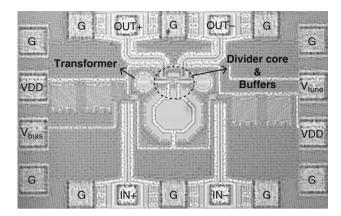

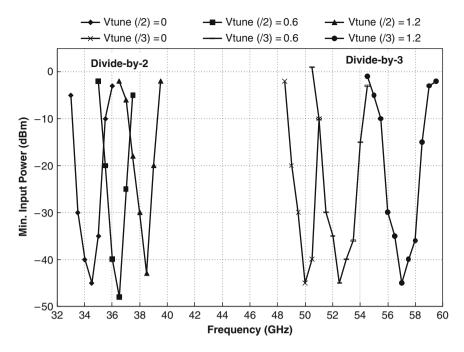

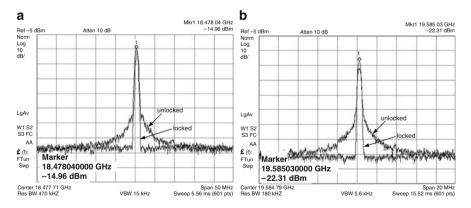

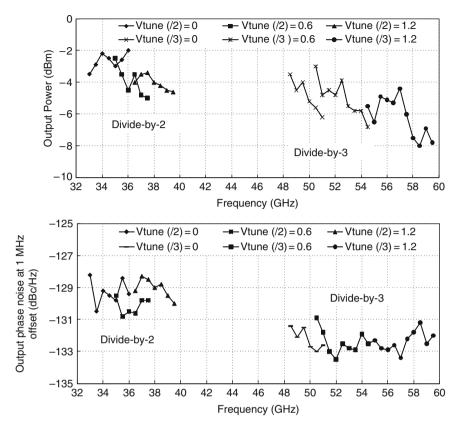

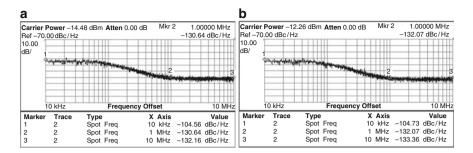

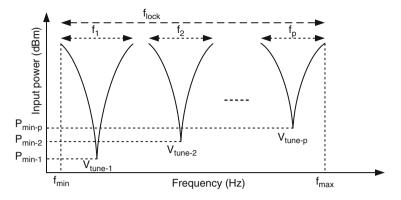

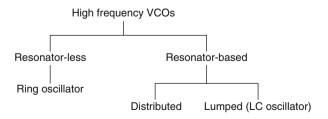

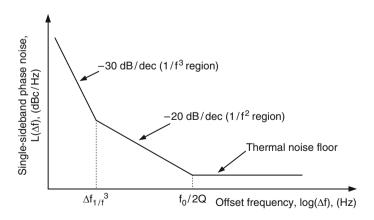

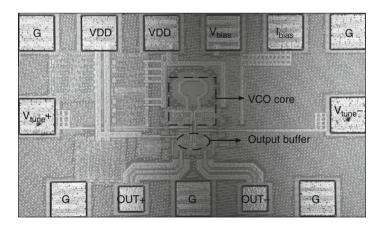

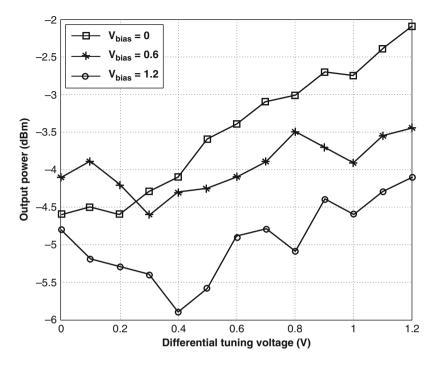

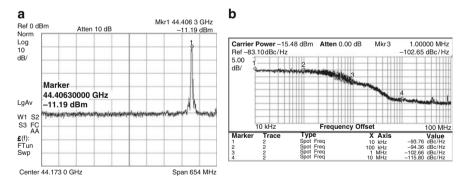

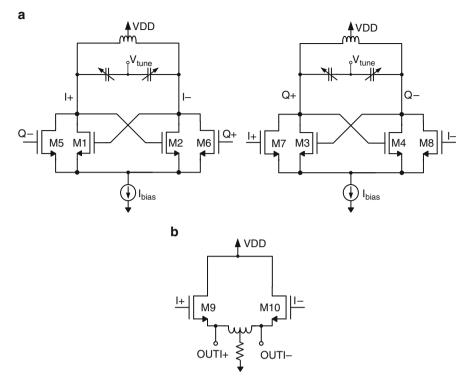

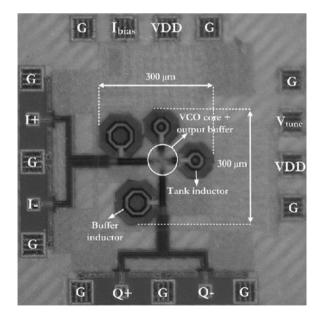

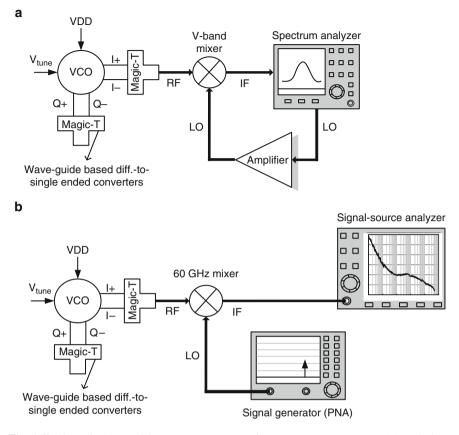

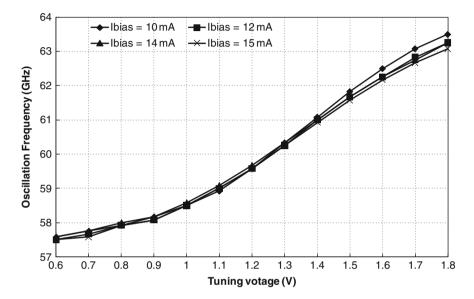

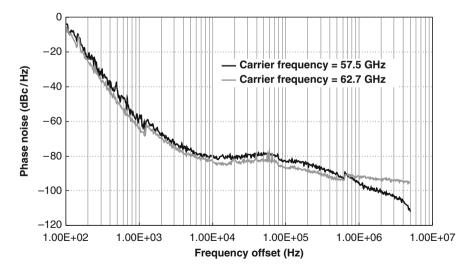

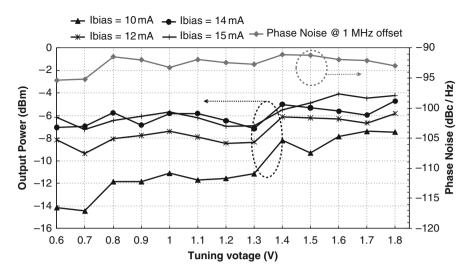

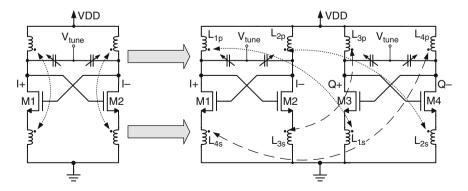

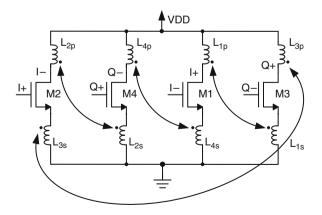

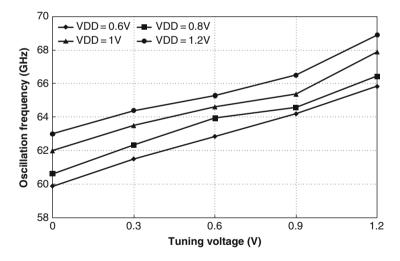

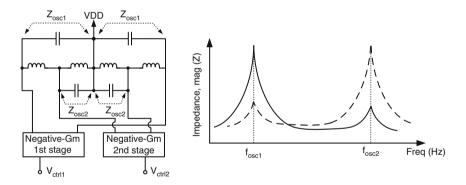

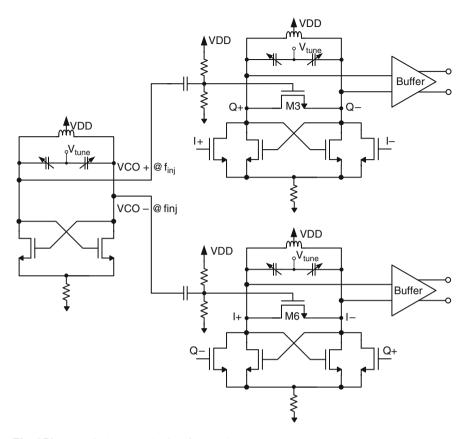

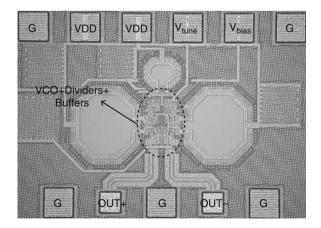

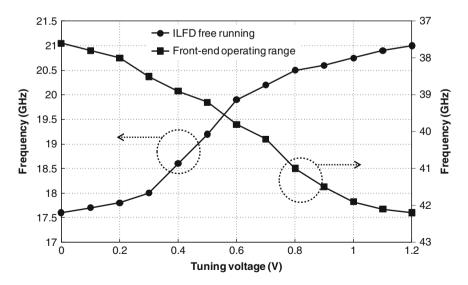

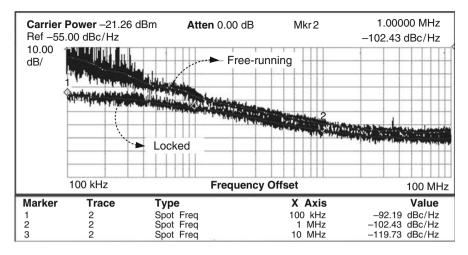

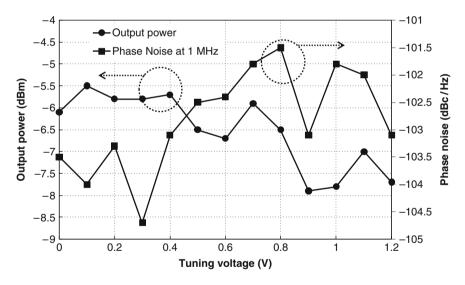

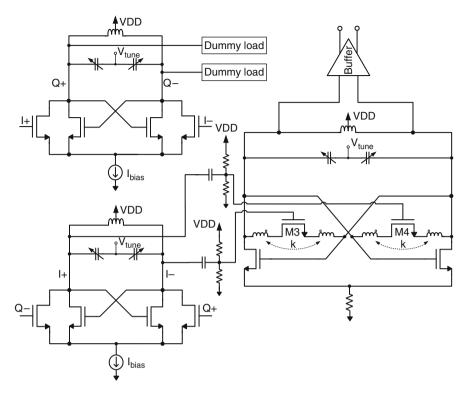

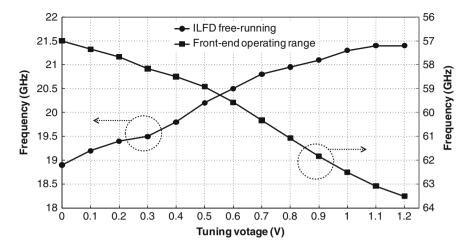

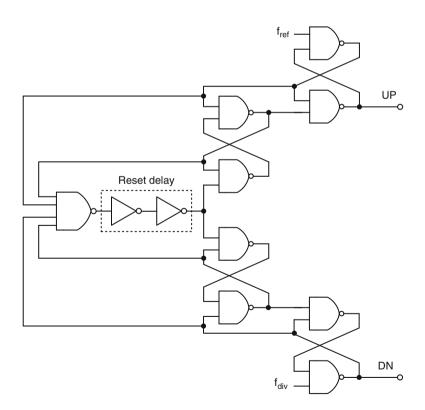

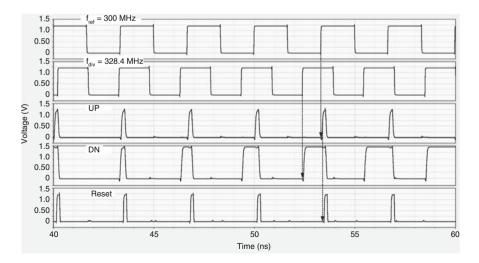

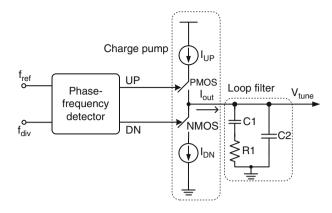

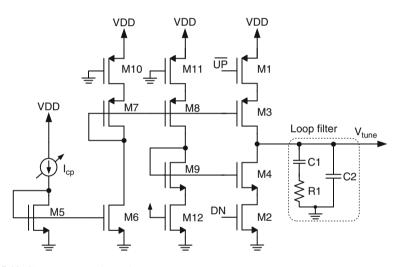

The overall phase noise characteristic of the synthesizer is formed by all the different circuits and components that make up the control loop. The noise contribution can be understood by Fig. 2.14 (slopes exaggerated for identification):